JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

2.1 デジタル電源

VCORE レギュレータ

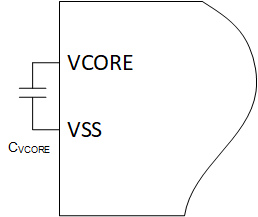

内部低ドロップアウト・リニア電圧レギュレータは、デバイス・コアに電力を供給するために 1.35V の電源レールを生成します。一般に、コア・レギュレータ出力 (VCORE) は CPU、デジタル・ペリフェラル、デバイス・メモリなどのコア・ロジックに電力を供給します。コア・レギュレータには、デバイスの VCORE ピンと VSS (グランド) の間に接続された外部コンデンサ (CVCORE) が必要です (図 2-1を参照)。CVCORE 正しい値と許容誤差については、デバイス固有のデータシートを参照してください。CVCORE は、VCORE ピンの近くに配置する必要があります。

コア・レギュレータは、シャットダウンを除くすべての電力モードでアクティブです。他のすべての電力モード (実行、スリープ、停止、スタンバイ) では、各モードの最大負荷電流をサポートするようにレギュレータの駆動能力が自動的に構成されます。これにより、低消費電力モード使用時のレギュレータの静止電流が減少し、低消費電力性能が向上します。

図 2-1 VCORE レギュレータ回路

図 2-1 VCORE レギュレータ回路