JAJA816E July 1994 – July 2021

6 バスホールド回路

フローティングバスに対して定義済のレベルを提供する最も効果的な方法は、選択したファミリがテキサスインスツルメンツ(TI™)のバスホールド機能を内蔵している部品か、またはSN74ACT1071やSN74ACT1073のような外部コンポーネントを使用することです(を参照表 6-1)。

| デバイス タイプ | 内臓バスホールド |

|---|---|

| SN74ACT1071 | クランプダイオード付きの 10 ビット・バスホールド |

| SN74ACT1073 | クランプダイオード付きの 16 ビット・バスホールド |

| ABT Widebus+(32 および 36 ビット) | すべてのデバイス |

| ABT Octals と Widebus | 選択したデバイスのみ |

| AHC/AHCT Widebus | TBA(選択したデバイスのみ) |

| 低電圧(LVTおよび ALVC) | すべてのデバイス |

| LVC Widebus | すべてのデバイス |

一部の TI ファミリではバスホールド回路を使用して、フローティング入力の問題を解決し、プルアップ抵抗およびプルダウン抵抗が不要になっています。バスホールド回路は 2 つの双方向インバータで構成され、出力は抵抗経由で入力にフィードバックされます(図 6-1を参照)。バスホールド回路の動作方法を理解するため、アクティブドライバがラインをハイレベルに切り替えたと仮定します。この場合、帰還回路に電流は流れません。これでドライバが HIGH インピーダンス状態になり、バスホールド回路が帰還抵抗を通じて High レベルを保持します。バスホールド回路の電流要件は、回路のリーク電流でのみ決まります。同じ条件は、バスが Low 状態のときに適用され、その後非アクティブになります。

図 6-1 代表的なバスホールド回路

図 6-1 代表的なバスホールド回路このセクションで説明したように、テキサスインスツルメンツは、VCCおよび GND にクランプダイオードを備えたスタンドアロンの 10 ビットおよび 16 ビットデバイス(SN74ACT1071およびSN74ACT1073)としてのバスホールド機能を提供しており、バス上のインピーダンスの不一致に起因するライン反射からの保護を強化します。CMOS 回路には純粋な抵抗を簡単に実装できないため、伝送ゲートと呼ばれる構成を帰還素子として使用します(図 6-2を参照)。N チャネルと P チャネルは、バッファ段の入力と出力との間に並列に配置されます。N チャネルトランジスタのゲートはVCCに接続され、P チャネルのゲートは GND に接続されます。バッファの出力が HIGH のとき P チャネルはオンで、出力が LOW のとき N チャネルはオンです。どちらのチャネルも表面積は比較的小さくなっています。ドレインからソースへのオン抵抗 RDSONは、約 5kΩ です。

図 6-2 スタンドアロンのバスホールド回路(SN74ACT107x)

図 6-2 スタンドアロンのバスホールド回路(SN74ACT107x)実用的なアプリケーションでは、バス上のドライバのリーク電流が IOZ = 10 mA であり、5-kΩ 抵抗の両端での電圧降下は VD = 0.8V であると仮定します(この値は、定義されたロジックレベルを保証するためのものと想定)。次に、バスホールド回路が処理できるコンポーネント部品の最大数は、式 6で計算されます。

74ACT1071および74ACT1073は、バスホールド回路への追加機能としてクランプダイオードも搭載しています。これらのダイオードは、ライン反射によって発生するオーバーシュートまたはアンダーシュートをクランプするのに役立ちます。図 6-3および図 6-4は、入力電圧が VCCを上回っている場合、または GND を下回っている場合のダイオードの特性を示しています。VI =-1V のとき、ダイオードは 50mA の電流を供給でき、アンダーシュートを除去するのに役立ちます。これは、ノイズの多いバスが問題である場合に非常に役立ちます。

| VCC = 5 V |

| VCC = 5 V |

TI は、一部の高度なファミリドライバおよびレシーバに追加する機能として、バスホールド回路も提供しています。この回路はスタンドアロン回路と似ていますが、2 番目のインバータのドレインにダイオードを追加します(ABTおよびLVTのみ、図 6-5を参照)。ダイオードは、入力電圧が VCC(V I > VCC)より高いときのオーバーシュート電流をブロックするため、リーク電流だけが存在します。この回路は、デバイスの入力段を 1 番目のインバータとして使用し、2 番目のインバータがフィードバック機能を生成します。バスホールド回路が処理できるコンポーネント部品の最大数の計算は、前の例と同様です。ただし、この回路をスタンドアロンのバスホールド回路と比較した場合の利点は、基板上のより多くの面積を占有する外付けの部品や抵抗が不要になることです。特にワイドバスを使用する場合、一部の設計ではこのことが重要になります。また、コストと基板寸法の制約が大きな問題となるため、設計者は修理の簡便性を好みます。つまり、直接差し替え可能な部品です。TI は、複数のファミリで一般的に使用される機能のほとんどでこの機能を提供しています(詳細については表 6-1を参照)。

図 6-5 バスホールド回路を搭載した ABT / LVT と ALVC/LVC ファミリの入力構造

図 6-5 バスホールド回路を搭載した ABT / LVT と ALVC/LVC ファミリの入力構造図 6-6と図 6-7は、入力電圧が 0 ~ 5V の範囲で掃引されているので、3.3-V および 5-V 動作におけるバスホールド回路の入力特性を示します。これらの特性は、弱いドライバと似ています。このドライバは入力が低いときにデバイスに電流をシンクし、入力が高いときにデバイスから電流を供給します。電圧がしきい値に近いとき、回路は常に入力を有効なレベルに維持しながら、他の状態への切り替えを試みます。これは、内部フィードバック回路の効果です。また、入力がしきい値に近いとき、電流が最大になることも示しています。II(hold)の最大値は、3.3-V 入力では約 25mA、5-V 入力では 400mAです。

図 6-6 V O—出力電圧—V バスホールド入力特性

図 6-6 V O—出力電圧—V バスホールド入力特性 図 6-7 V I—入力電圧—V バスホールド入力特性

図 6-7 V I—入力電圧—V バスホールド入力特性バスホールド回路を備えた複数のデバイスが単一のドライバで駆動される場合、ドライバの AC スイッチング能力が弱くなる懸念が生じる可能性があります。小型ドライバなので、バスホールド回路はスイッチングのために AC 電流を必要とします。TI の CMOS および BiCMOS ファミリを使用している場合、この電流は重要ではありません。図 6-8に、6 つのLVTH16244デバイスを駆動する 4-mA バッファを示します。このトレースは 75Ω の伝送経路です。レシーバは 1cm 離れており、ドライバはトレースの中央に配置されています。図6-9および図6-10は、6 つのレシーバを Low または High に切り替えたときのドライバに対するバスホールドの負荷効果を示しています。図6-9および図6-10は、同じシステムのバスホールド回路がレシーバから切断された状態を示しています。どちらのプロットも、ドライバの立ち上がり時間と立ち下がり時間に対するバスホールドの影響を示しています。当初、バスホールド回路はドライバを打ち消そうとするため、立ち上がりまたは立ち下がり時間が長くなります。その後、バスホールド回路の状態が変化し(クロスオーバーポイントに注意)、ドライバの切り替えを高速化し、立ち上がりまたは立ち下がり時間の短縮に寄与します。

図 6-8 ドライバおよびレシーバ機能

図 6-8 ドライバおよびレシーバ機能

| VCC = 3.3 V | TA = 25℃ |

| VCC = 3.3 V | TA = 25℃ |

図6-11に、入力を 0 ~ 5V の範囲で掃引したときのバスホールド回路の電源電流(ICC)を示します。約 1.5-V VIのスパイクは、N チャネルと P チャネルの両方が同時に導通していることに起因しています。これは CMOS トランジスタの特性の 1 つです。

| VCC = 5 V |

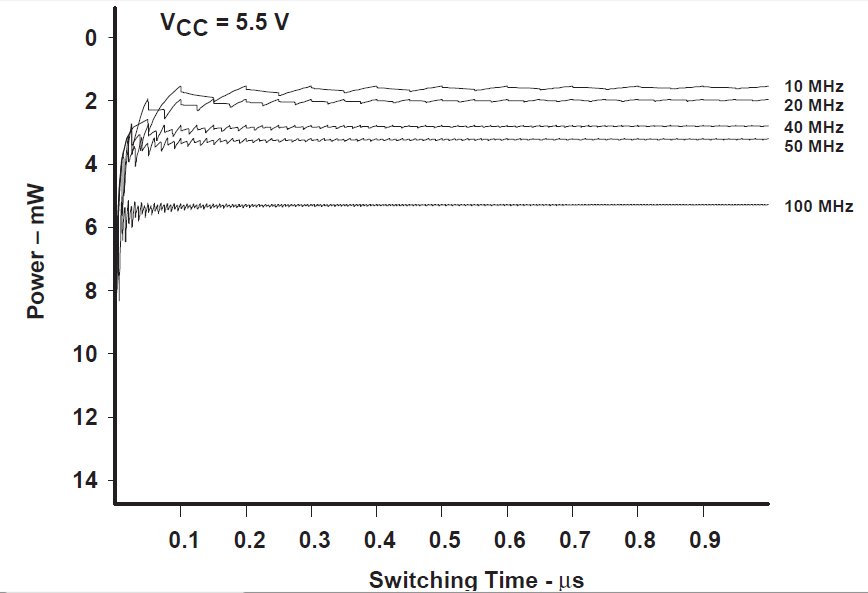

より高い周波数で入力をスイッチングすると、バスホールド回路の消費電力は最小限に抑えられます。図 6-12バスホールドあり/なしでの、さまざまな周波数で入力したときの消費電力を、図 6-13に示します。高い周波数によるバスホールド回路の消費電力の増加は、電力計算で考慮するほどの大きさにはなりません。

図 6-12 さまざまな周波数におけるバスホールド入力電力のプロット

図 6-12 さまざまな周波数におけるバスホールド入力電力のプロット 図 6-13 バスホールドがない場合のさまざまな周波数における入力電力のプロット

図 6-13 バスホールドがない場合のさまざまな周波数における入力電力のプロット表 6-2に、バスホールドのデータシートのDC仕様を示します。最初のテスト条件は、バスを 0.8V または 2V に保持するために必要な最小電流です。これらの電圧は、TTL 入力で規定された Low および High レベルを満たしています。2 番目のテスト条件は、0V ~ 3.6V(低電圧ファミリの場合)または 0V ~ 5.5V(ABTの場合)の任意の入力電圧で、バスホールド回路がソースまたはシンクする最大電流です。入力電圧がレール電圧に近づくと、バスホールド電流は最小限に抑えられます。バスホールド付きのトランシーバでは、出力リーク電流IOZHとIOZLは重要ではありません。バスホールド回路の存在により真のリークテストを実行できないためです。バスホールド回路は小型のドライバとして動作するため、リーク電流とは逆方向になる電流をソースまたはシンクする傾向があります。この状況は、バスホールド機能を備えたトランシーバにのみ当てはまり、バッファには適用されません。すべてのLVT、ABT Widebus+、選択されたABTオクタルおよび Widebus デバイスには、バスホールド機能が備わっています(詳細については最寄りのテキサスインスツルメンツ販売代理店にお問い合わせください)。表 6-1

| 最小値 | 最大値 | 単位 | |||||

|---|---|---|---|---|---|---|---|

| II(hold) | データ入力または I/O | LVT、 LVC、ALVC | VCC = 3 V | VI = 0.8 V | 75 | µA | |

| VI = 2 V | -75 | ||||||

| LVC、ALVC | VCC = 3.6 V | VI = 0~3.6V | ±500 | ||||

| ABT Widebus+ および選択したABT | VCC = 4.5 V | VI = 0.8 V | 100 | ||||

| VI = 2 V | -100 | ||||||

| IOZH/IOZL | バスホールド機能を搭載したトランシーバ | ABT | バスホールドは常に I/O ピンでアクティブなので、このテストは真の IOZテストとはなりません。バスホールドは、出力リーク電流とは逆方向の電流を供給する傾向があります。 | ±1 | µA | ||

| LVT、 LVC、ALVC | |||||||

| バスホールド付きのバッファ | ABT | 出力ピンにはバスホールドが存在しないため、このテストは真の OZテストとなります。 | ±10 | ||||

| LVT、 LVC、ALVC | ±5 | ||||||