SLAT161 June 2022 HD3SS3411 , TMUXHS4412

2.2.2 Data Reference Clock

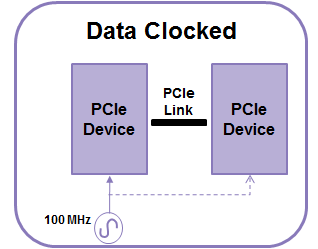

Figure 2-3 shows the Data refclk architecture. The Data refclk architecture is the simplest to implement since it only requires one clock source located at the transmitter. Although the Data refclk architecture has a simpler block diagram, its jitter requirements are more difficult to meet because less filtering is applied. The data refclk architecture is only supported in PCIe Gen 2 and Gen 3.

Figure 2-3 Data Clock

Architecture

Figure 2-3 Data Clock

Architecture