SPRAD03 March 2022 AM2431 , AM2431 , AM2432 , AM2432 , AM2434 , AM2434 , AM6411 , AM6411 , AM6412 , AM6412 , AM6421 , AM6421 , AM6422 , AM6422 , AM6441 , AM6441 , AM6442 , AM6442

- Trademarks

- 1 System Overview

- 2 Hardware Prerequisites

- 3 Hardware Configuration

- 4 HW Pinouts, Default Jumpers, and Connections

- 5 Schematics

- 6 Jumper Settings and Descriptions

- 7 LEDs

- 8 Software Architecture

- 9 Actuation and Feedback Timing

- 10Benchmark Results

-

11Detailed Demo User's Guide

- 11.1 Step 0. Getting the Software and Building

- 11.2 Step 1. Getting Started With the Hardware

- 11.3 Step 2. Configure ROQ437 EnDat2.2 Encoder for Faster EnDat 2.2 Recovery Time (only needs to be done once the first time you use the ROQ437 encoder)

- 11.4 Step 3. Open Loop Iq Control (BUILDLEVEL == OPEN_LOOP_IQ_ID)

- 11.5 Step 4. Closed Loop Iq/Id Control (BUILDLEVEL == CLOSED_LOOP_IQ_ID)

- 11.6 Step 5. Closed Loop Speed Control (BUILDLEVEL == CLOSED_LOOP_SPEED)

- 11.7 Step 6. Closed Loop Position Control (BUILDLEVEL == CLOSED_LOOP_POSITION)

- 12Build Using MCU+SDK 08.00.00.21 & CCS 10.3.1

- 13Summary

- 14Appendix A: Detailed Motor Control R5F Processing Time

- 15References

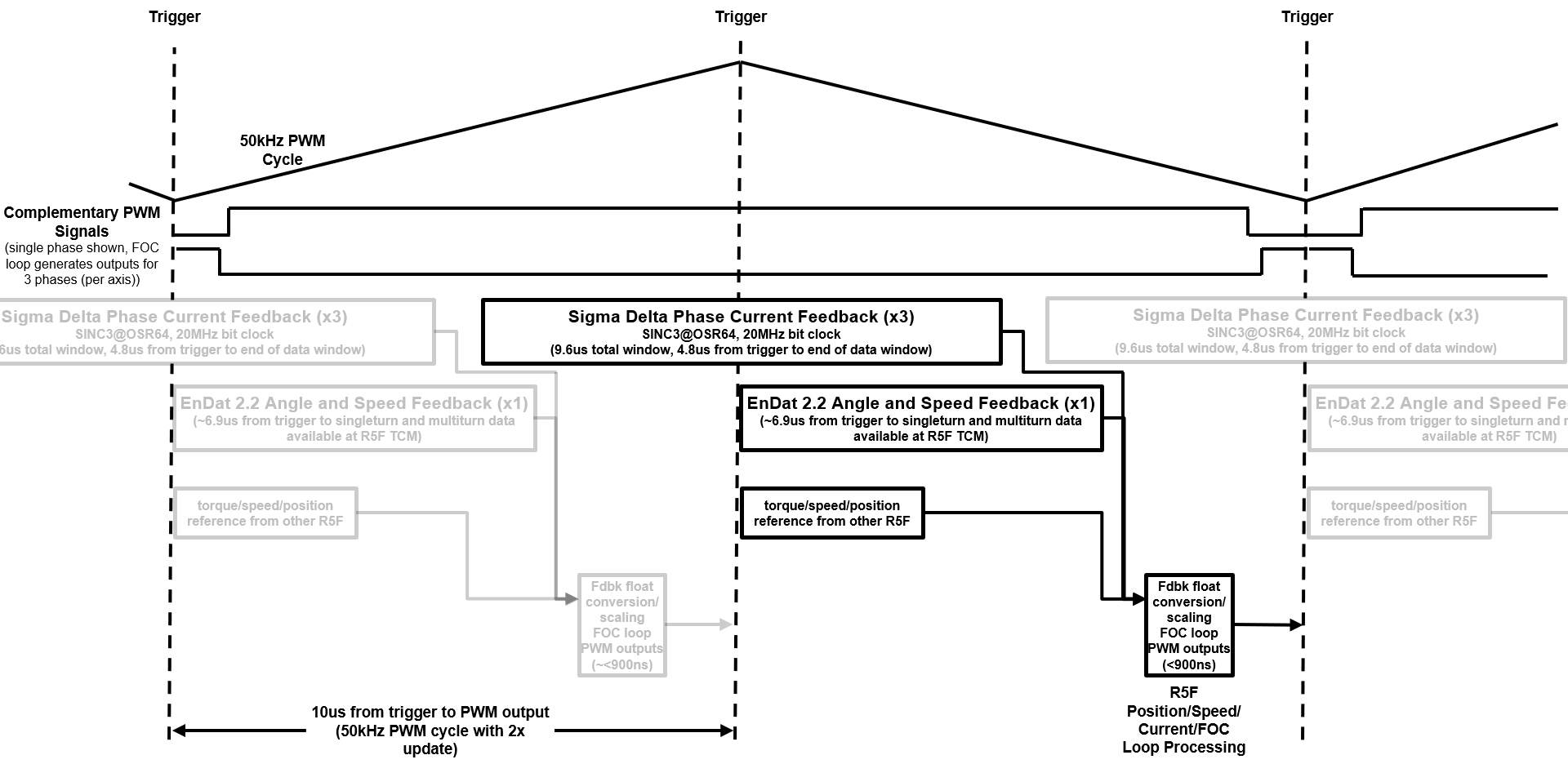

9 Actuation and Feedback Timing

The precision of the actuation and feedback timing in the demo is crucial to the correct performance of the FOC loop calculations and in turn the overall motor control performance. To achieve the goal, this demo setup is as follow:

- 50 KHz PWM cycle time

- PWM resolution of greater

than 12 bits achieved due to EPWM peripheral clocking at 250 MHz

- 50 KHz / 4 ns = 5000, which equates to approximately 12.28 bits of resolution

- PWM resolution of greater

than 12 bits achieved due to EPWM peripheral clocking at 250 MHz

- 100 KHz FOC loop update

- 2x updates per PWM cycle

- Allows for 10 µs from trigger point until feedback can be captured, FOC loop close, and PWM values updated in the shadow registers

- Achieved timing diagram

here:

Figure 9-1 Timing

Diagram

Figure 9-1 Timing

Diagram

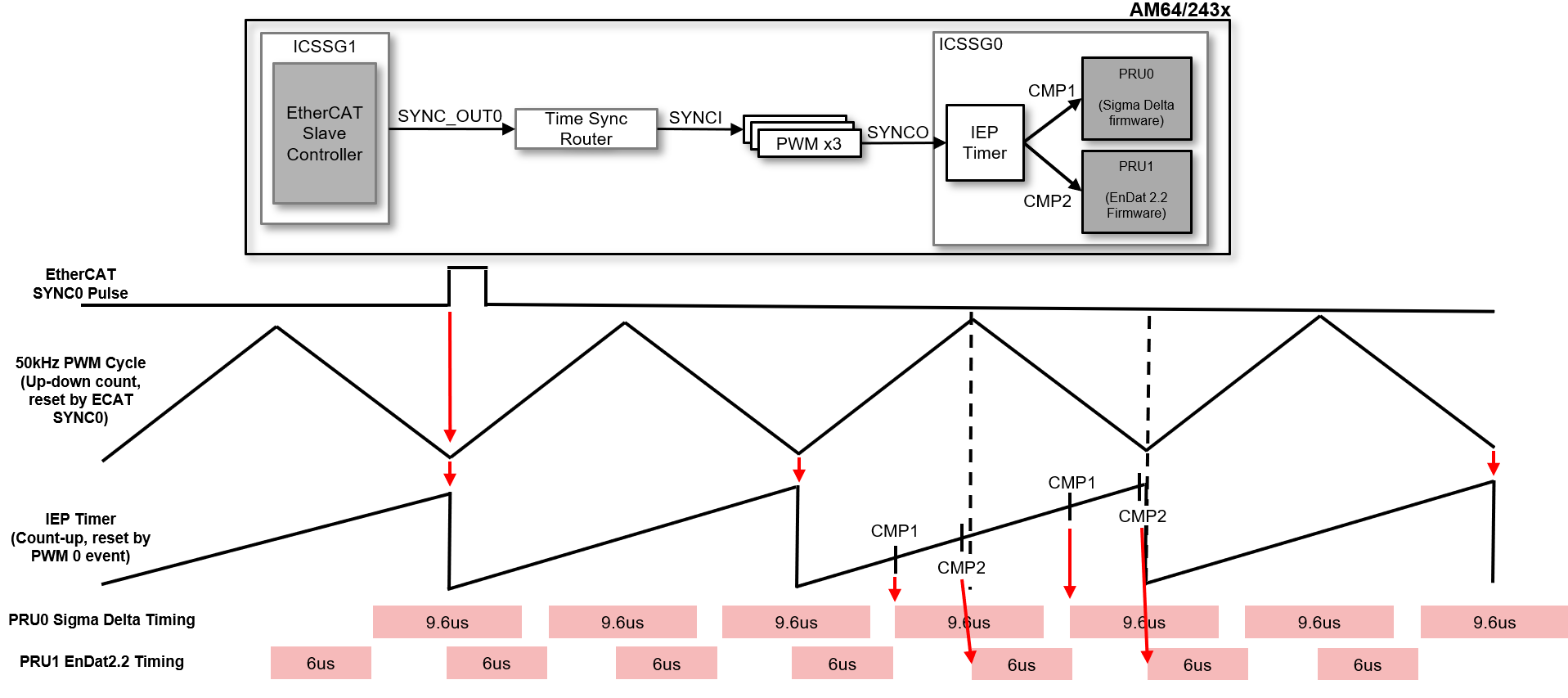

- Precise triggering for both

EnDat2.2 and Sigma Delta feedback data

- A synchronization technique between the PWM peripheral and the IEP Timer of ICSSG0 is used in order to precisely place the triggers anywhere along the PWM cycle

- EPWM SYNCO signal resets

the IEP Timer counter and CMP1 and CMP2 values are used to trigger the

start points for both EnDat and Sigma Delta

Figure 9-2 Synchronization Techniques

Figure 9-2 Synchronization Techniques - Technique visualized below and results shown in 'Benchmark results' section