TIDT319 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

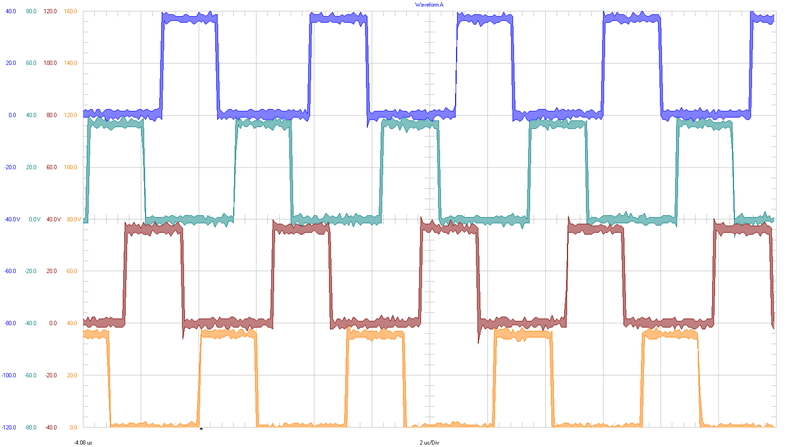

- 3Waveforms for 2 × LM5143A-Q1 in Four Phase Configuration and Interleaved Operation

- A Individual Adjusting of the Rising Edge and Falling Edge With LM5143A

- B Measurements Across the Low-Side FETs to Check at All Four Phases

- C ON Demand – Assembly of Thermal Interface