TIDT319 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms for 2 × LM5143A-Q1 in Four Phase Configuration and Interleaved Operation

- A Individual Adjusting of the Rising Edge and Falling Edge With LM5143A

- B Measurements Across the Low-Side FETs to Check at All Four Phases

- C ON Demand – Assembly of Thermal Interface

1.2 Considerations

Unless otherwise indicated, all measurements were done with 24-V input voltage and 50-A output current.

The load used was an electronic load TDI RBL100-120-800, limited to 800 WMAX, squeezed up to 828 W; the source was the SMPS Agilent 6574A, limited to a maximum 35-A input current, squeezed up to 35.8 A.

Efficiency and thermal image measurements up to 60-A continuous current are provided, but with a proper thermal interface there is still some headroom left – the current limitation trips at around 70 A.

Unless otherwise indicated, an air flow of 0.5 meters per second (m/s) to 1 m/s was used for the first measurements.

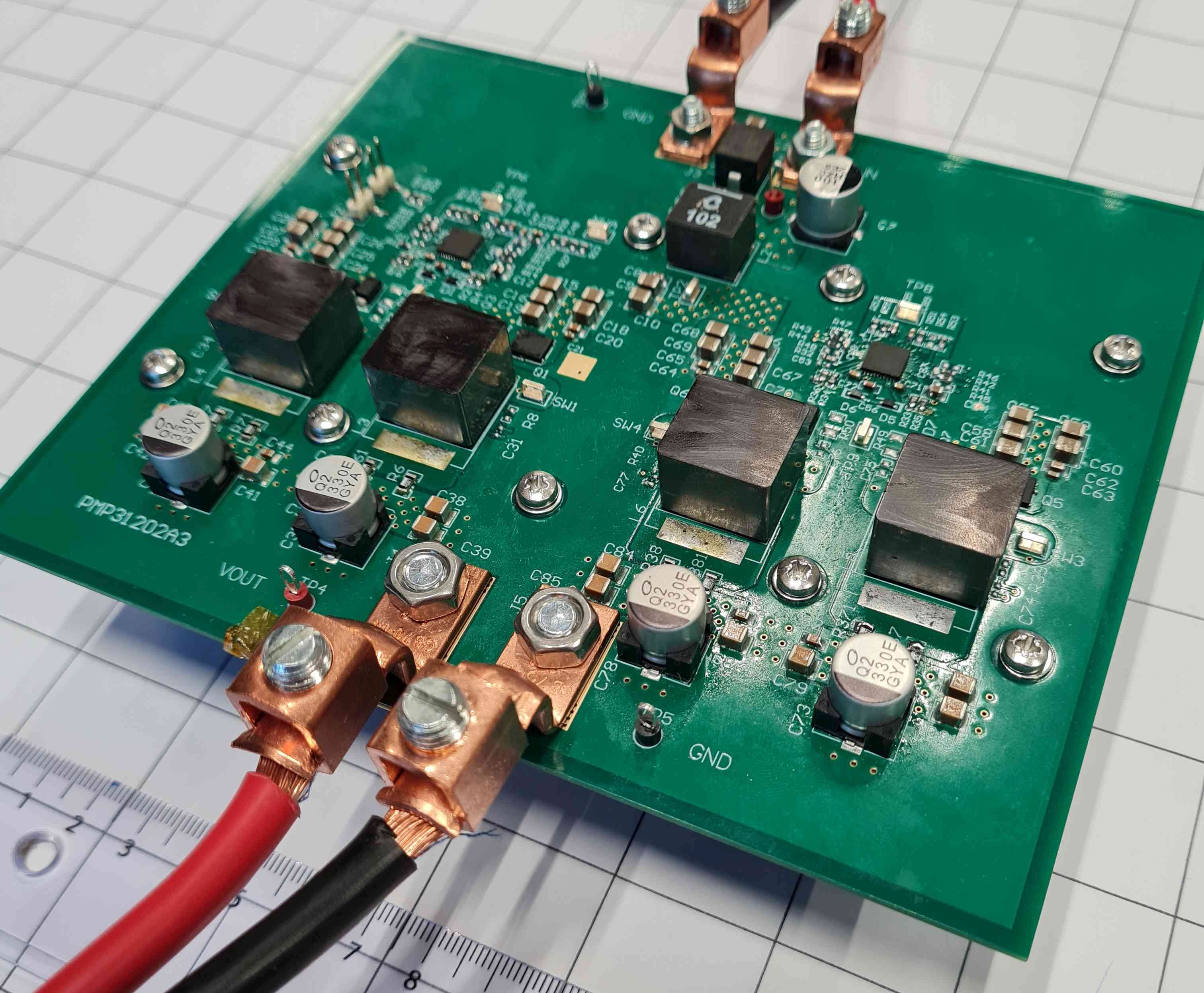

Figure 1-1 Board Image With Connected

Cable

Figure 1-1 Board Image With Connected

Cable