TIDT328 april 2023

A.2.3.1 DC-Bias

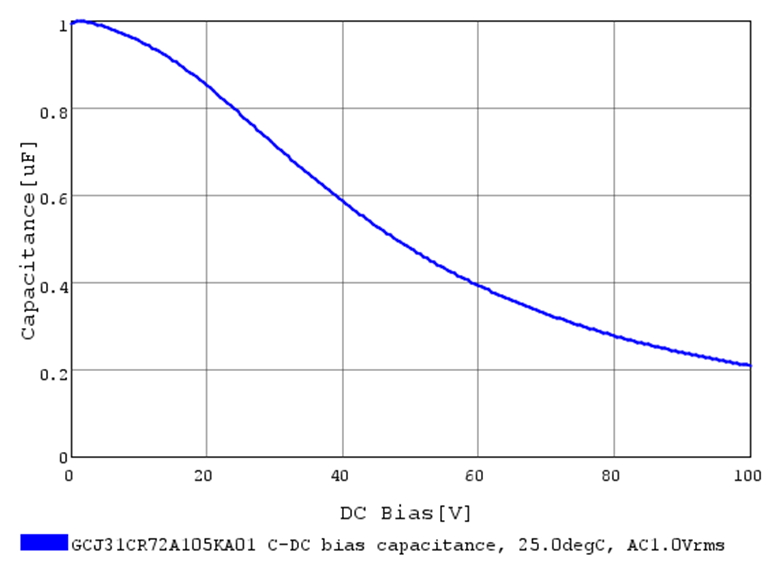

Figure 4-13 Effective Capacitance vs DC

Bias

Figure 4-13 Effective Capacitance vs DC

BiasFigure 4-13 illustrates that with 60-VDC output voltage the effective capacitance

of the 1-µF capacitor is just

400 nF.

TIDT328 april 2023

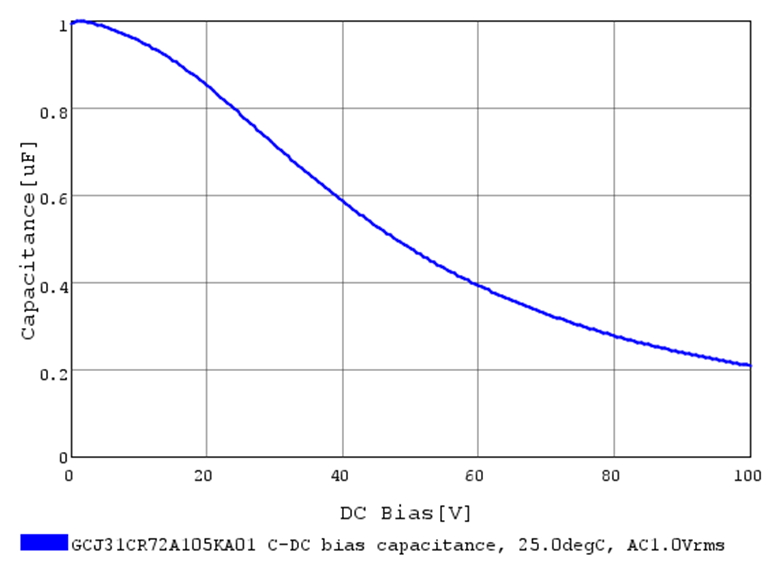

Figure 4-13 Effective Capacitance vs DC

Bias

Figure 4-13 Effective Capacitance vs DC

BiasFigure 4-13 illustrates that with 60-VDC output voltage the effective capacitance

of the 1-µF capacitor is just

400 nF.