TIDT328 april 2023

3.1.1.2 Gate to Source

|

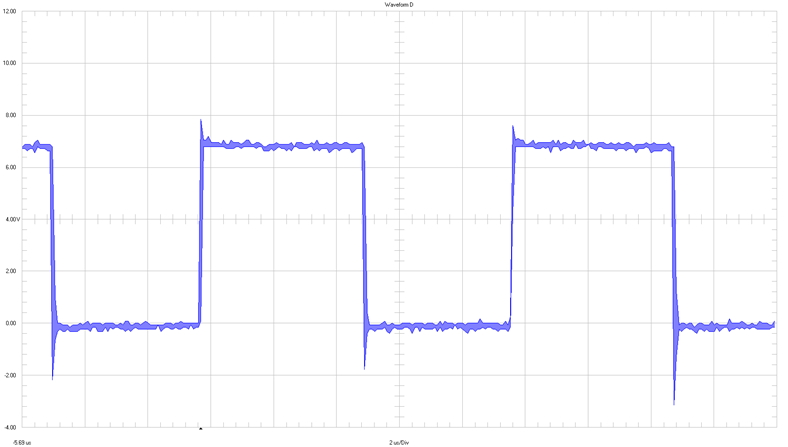

2 V / div 2 µs / div full bandwidth |

|

|

|

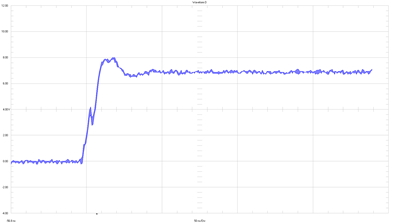

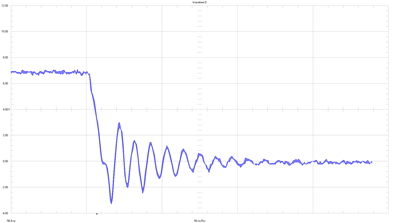

2 V / div 250 ns full scale full bandwidth |

Figure 3-2 Switching Q1

(Gate-Source)