DLPU133 March 2024 DLPC964

- 1

- Abstract

- Trademarks

- 1Overview

-

2Apps FPGA

Modules

- 3.1 Apps FPGA Block Diagram

- 3.2 BPG Module

- 3.3 BRG Module

- 3.4 BRG_ST Module

- 3.5 PGEN Module

- 3.6 PGEN_MCTRL Module

- 3.7 PGEN_SCTRL Module

- 3.8 PGEN_PRM Module

- 3.9 PGEN_ADDR_ROM

- 3.10 HSSTOP Module

- 3.11 SSF Module

- 3.12 ENC Module

- 3.13 Xilinx IP

- 3.14 Reference Documents

- 3.15 DLPC964 Apps FPGA IO

- 3.16 Key Definitions

- 3Functional Configuration

-

4Appendix

- 5.1 Vivado Chipscope Captures

- 5.2 DLPC964 Apps Bitstream Loading

- 5.3

Interfacing To DLPC964 Controller with Aurora

64B/66B

- 5.3.1 Theory of Operation

- 5.3.2 Overview

- 5.3.3

Aurora 64B/66B TX Core and RTL Generation

- 5.3.3.1 Select Aurora 64B66B From IP Catalog

- 5.3.3.2 Configure Core Options

- 5.3.3.3 Lane Configurations

- 5.3.3.4 Shared Logic Options

- 5.3.3.5 Generate Example Design Files

- 5.3.3.6 RTL File List

- 5.3.3.7 Single Channel 3 Lanes Aurora Core RTL Wrapper

- 5.3.3.8 Four Channels 12 Lanes Top Level RTL Wrapper

- 5.3.3.9 Block Start with Block Control Word

- 5.3.3.10 Block Complete with DMDLOAD_REQ

- 5.3.3.11 DMDLOAD_REQ Setup Time Requirement

- 5.3.3.12 Single Channel Transfer Mode

- 5.3.3.13 DMD Block Array Data Mapping

- 5.3.3.14 Xilinx IBERT

- 5Abbreviations and Acronyms

- 6Related Documentation from Texas Instruments

2.16 Key Definitions

- Block - A block is a 136 lines x 4096 pixels portion of the DMD. The DMD is split into 16 of these blocks making the total image size of the DMD 2176 lines x 4096 pixels. Blocks can be individually addressed (0x0 - 0xF) in the DLPC964 Apps FPGA.

- Segment - There are four segments (A,B,C, and D) per block. Each segment consists of 136 lines x 1024 pixels. In normal operation, each of the 4 segments are loaded at the same time. In slow mode each segment are loaded individually.

- Groups - When in double or quad modes, blocks are updated in groups. These groups are outlined in the table below. Note the importance that the user either enables all blocks in a group or disabled all blocks in a group when in double or quad modes.

| Block Load Address | 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF |

| Double Mode Groups | 0x0 | 0x2 | 0x4 | 0x6 | 0x8 | 0xA | 0xC | 0xE | ||||||||

| Quad Mode Groups | 0x0 | 0x4 | 0x8 | 0xC | ||||||||||||

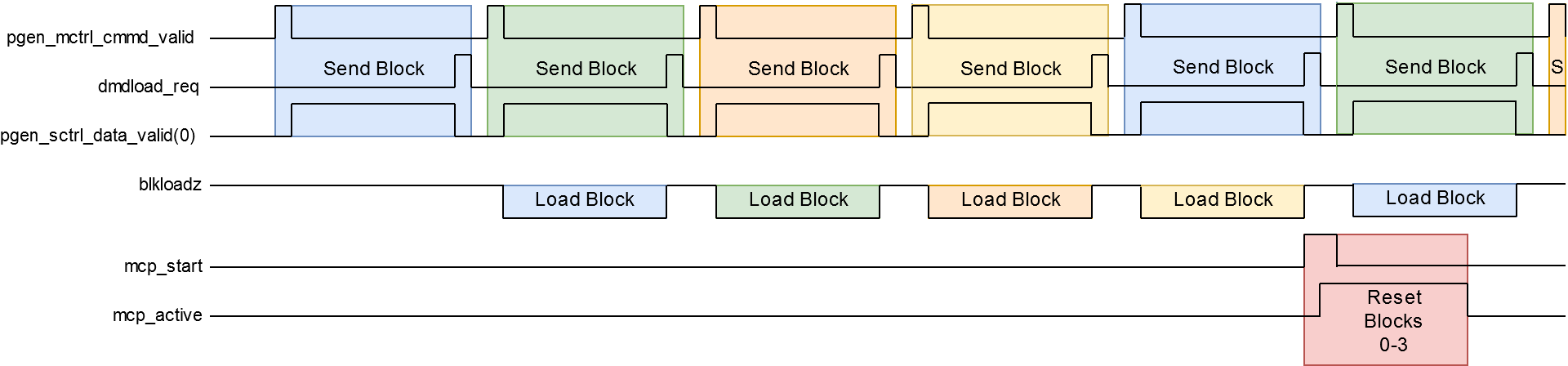

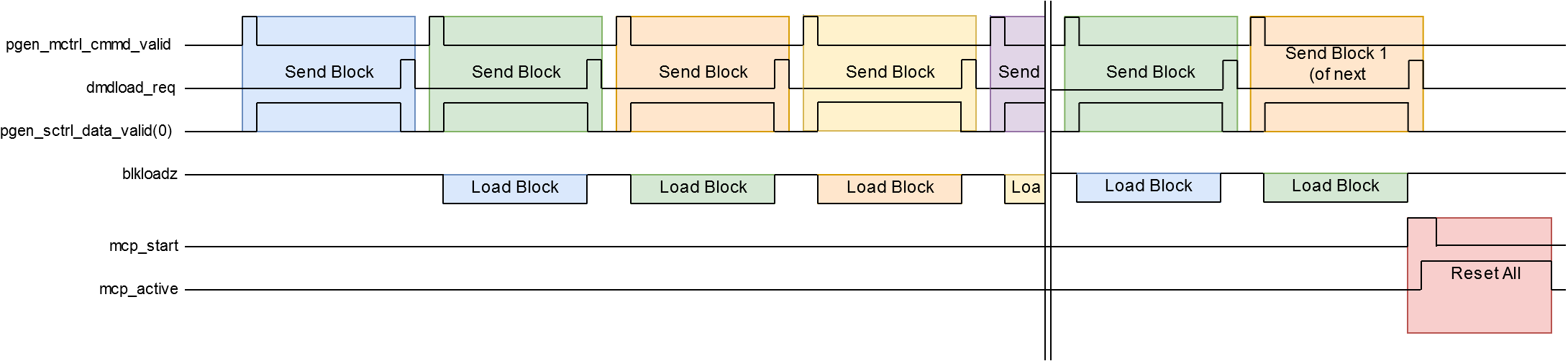

Below are simple timing examples of sending blocks in x4 mode and global mode.

Figure 2-9 x4 Mode

Figure 2-9 x4 Mode Figure 2-10 Global Mode

Figure 2-10 Global Mode- DLPC964 Apps - The Xilinx VC707 loaded with the Apps FPGA bitstream.

- DLPC964 - The DLPC964 Controller that interfaces with the DMD.

- Modes - There are 4 modes: Single (0x0), Double or x2 (0x1), Quad or x4 (0x2), and Global (0x3). These modes are explained in more detail below and in Section 3.

- Single (0x0) - In single mode, each block is loaded with data and once the DLPC964 has finished loading that individual block onto the DMD, the DMD is updated with the MCP_Start signal. Since each block can be updated individually, the valid block mode addresses are 0x0 - 0xF.

- Double (0x1) - Double mode

means that once the DLPC964 has loaded 2 blocks within a group with data, the

DMD updates both of these blocks with a single MCP_Start signal. Since 2 blocks

are updated at a time, the valid block mode address are 0x0, 0x2, 0x4, 0x6, 0x8,

0xA, 0xC, and 0xE. Note: Note the importance to know that when enabling and disabling blocks in double mode, all blocks within a group must be enabled or disabled.

- Quad (0x2) - Quad mode means that once the DLPC964 has loaded 4 blocks within a group with data, the DMD updates all 4 blocks with a single MCP_Start signal. Since 4 blocks are updated at a time, the valid block mode address are 0x0, 0x4, 0x8, and 0xC.

- Global (0x3) - This is the

default startup mode. In global mode, all enabled blocks are loaded and once the

DLPC964 has finished, the MCP_Start signal updates all the blocks at once. Since

all the blocks have been updated at once, the next load operation needs to wait

until the mirrors have settled. Note: This is known as the mirror settle time and must be around 8 us.

- Block Load Type - The block load type is sent before the data using the user-k in the Aurora GTX interface. The DMD supports 3 different types of loads; Normal (0x0), Clear (0x1), and Set (0x2).

- Normal (0x0) - This is the default block load type. The Normal load type tells the DLPC964 to load the DMD with whatever data comes after the user-k data.

- Clear (0x1) - Clear load type does not send any data. This is because when the DLPC964 receives a clear load type, the DLPC964 sets the mirrors in the block specified to the off state (0).

- Set (0x2) - Set load type does not send any data. This is because when the DLPC964 receives the set load type, the DLPC964 sets the mirrors in the block specified to the on start (1).

- MCP_Start - The MCP_Start (Mirror Clocking Pulse Start) signals the DMD to update the mirrors with whatever data was sent. The DLPC964 determines which blocks to update based on the Mode selected and the block mode address.

- Lines/Rows - A line of pixels refers to the horizontal row of pixels 4096 across. Think of this as the y-position on the DMD.

- Pixels/Columns - A column of pixels refers to the vertical column of pixels 2176 across. Think of this as the x-position on the DMD.

- Fast/Slow Mode - Fast mode by default is enabled. Fast mode refers to sending all 4 segments of a block in parallel across the 4 Aurora GTX channels. Slow mode uses only the first GTX channel and sends the segments sequentially. Refer to the Pattern Modes section for more details on the segment ordering.

- Load2 Mode - Load2 is disabled by default. When in Load2 mode, the DLPC964 Apps only sends half of the number of rows specified (136 lines requested, only 68 are sent). This is because in this mode, the DMD loadS every 2 lines with the same data.