DLPU133 March 2024 DLPC964

- 1

- Abstract

- Trademarks

- 1Overview

-

2Apps FPGA

Modules

- 3.1 Apps FPGA Block Diagram

- 3.2 BPG Module

- 3.3 BRG Module

- 3.4 BRG_ST Module

- 3.5 PGEN Module

- 3.6 PGEN_MCTRL Module

- 3.7 PGEN_SCTRL Module

- 3.8 PGEN_PRM Module

- 3.9 PGEN_ADDR_ROM

- 3.10 HSSTOP Module

- 3.11 SSF Module

- 3.12 ENC Module

- 3.13 Xilinx IP

- 3.14 Reference Documents

- 3.15 DLPC964 Apps FPGA IO

- 3.16 Key Definitions

- 3Functional Configuration

-

4Appendix

- 5.1 Vivado Chipscope Captures

- 5.2 DLPC964 Apps Bitstream Loading

- 5.3

Interfacing To DLPC964 Controller with Aurora

64B/66B

- 5.3.1 Theory of Operation

- 5.3.2 Overview

- 5.3.3

Aurora 64B/66B TX Core and RTL Generation

- 5.3.3.1 Select Aurora 64B66B From IP Catalog

- 5.3.3.2 Configure Core Options

- 5.3.3.3 Lane Configurations

- 5.3.3.4 Shared Logic Options

- 5.3.3.5 Generate Example Design Files

- 5.3.3.6 RTL File List

- 5.3.3.7 Single Channel 3 Lanes Aurora Core RTL Wrapper

- 5.3.3.8 Four Channels 12 Lanes Top Level RTL Wrapper

- 5.3.3.9 Block Start with Block Control Word

- 5.3.3.10 Block Complete with DMDLOAD_REQ

- 5.3.3.11 DMDLOAD_REQ Setup Time Requirement

- 5.3.3.12 Single Channel Transfer Mode

- 5.3.3.13 DMD Block Array Data Mapping

- 5.3.3.14 Xilinx IBERT

- 5Abbreviations and Acronyms

- 6Related Documentation from Texas Instruments

4.3.3.9 Block Start with Block Control Word

Aurora is a generic data transport link without concept of a DMD block. To define the start of a DMD block, the Apps user logics must send a Block Control word packet through channel 0 Aurora user-k port before data transmission.

Refer to Xilinx app note Chapter 2 Table 2-10 for detailed information regarding the Aurora user-k interface port. In summary, the user-k interface ports are used to implement application-specific control functions, and are independent and higher priority than the data interface. As shown in Table 4-2 , the RTL wrapper aurora_apps_tx_x12ln.v has four channels of user-k port interface exposed to Apps FPGA user logics.

| Signal Name | Signal Direction | DLPC964 Application Usage |

|---|---|---|

| gt0_s_axi_user_k_tx_tdata[191:0] | Input to Aurora Channel 0 | 192 bits Block Control word packet to be trasmitted |

| gt0_s_axi_user_k_tx_tvalid | Input to Aurora Channel 0 |

User logics asserted this signal high to indicate to Aurora core the Block Control word is valid to transmit. Aurora cores ignore word if tvalid is low. |

| gt0_s_axi_user_k_tx_tready | Output from Aurora Channel 0 |

Aurora cores assert this signal high when the Block Control word is accepted. Deasserted when words are ignored, ie. cores are not ready to accept input word. |

| gt1_s_axi_user_k_tx_tdata[191:0] | Input to Aurora Channel 1 | Unused |

| gt1_s_axi_user_k_tx_tvalid | Input to Aurora Channel 1 | Unused |

| gt1_s_axi_user_k_tx_tready | Output from Aurora Channel 1 | Unused |

| gt2_s_axi_user_k_tx_tdata[191:0] | Input to Aurora Channel 2 | Unused |

| gt2_s_axi_user_k_tx_tvalid | Input to Aurora Channel 2 | Unused |

| gt2_s_axi_user_k_tx_tready | Output from Aurora Channel 2 | Unused |

| gt3_s_axi_user_k_tx_tdata[191:0] | Input to Aurora Channel 3 | Unused |

| gt3_s_axi_user_k_tx_tvalid | Input to Aurora Channel 3 | Unused |

| gt3_s_axi_user_k_tx_tready | Output from Aurora Channel 3 | Unused |

Table 4-3 describes the various fields within the 192 bits Block Control word. Block Control word not only defines the start of a DMD block, but also contains instruction and information to guide the DLPC964 controller on how to process the receiving DMD block data

| Field Position | Field Type | Field Description |

|---|---|---|

| gt0_s_axi_user_k_tx_tdata[7:0] | USER_BLOCK_NUMBER | Must set to zeros (0x00). Values other than 0x00 are invalid, DLPC964 controller ignores the entire 192 bits control word if this field is not zeros. |

| gt0_s_axi_user_k_tx_tdata[11:8] | BLOCK_ADDRESS |

Indicates the address of the DMD block to which DLPC964 applies the operation. 0000: DMD Block 0 0001: DMD Block 1, 0010: DMD Block 2 ….…. 1111: DMD Block 15 |

| gt0_s_axi_user_k_tx_tdata[15:7] | Reserved, unused. | |

| gt0_s_axi_user_k_tx_tdata[24:16] | ROW_LENGTH | Number of row DLPC964 loads the user

data. DLP991U DMD has 136 rows per block, thus valid range is 1-136.

All other values, including 0 are invalid. Set to 136 for full block

operation. Value 1 to 135 for partial block. Note: This field used if LOAD_TYPE is

000. |

| gt0_s_axi_user_k_tx_tdata[34:32] | LOAD_TYPE |

000: Block loading. DLPC964 load the user data to the DMD array area defined by the BLOCK_ADDRESS and ROW_LENGTH. 001: Block clear. DLPC964 clear the DMD array to zeros of the entire block define by BLOCK_ADDRESS. 010: Block set. DLPC964 set the DMD array to ones of the entire block defined by BLOCK_ADDRESS. Other values: reserved, do not use. Note: When in 001 (block clear) or 010 (block

set) operation, the ROW_LENGTHand NORTH_SOUTH_FLIP fields are

ignored because clear and set operation affect the entire DMD

block array. In other words, block set/clear operation do not

support partial block operation.

|

| gt0_s_axi_user_k_tx_tdata[36] | NORTH_SOUTH_FLIP |

Control the direction of data loading within a DMD block. 0: DLPC964 load data starting and counting up from row 1. 1: DLPC964 load data starting and counting down from row 136. |

| gt0_s_axi_user_k_tx_tdata[29:28] | DMD_SEGMENT |

When SINGLE_CHANNEL_MODE = '1', select the DMD segment to which the DLC964 applies the operation. DLPC964 Controller ignores this field if SINGLE_CHANNEL_MODE = '0'. |

| gt0_s_axi_user_k_tx_tdata[30] | SINGLE_CHANNEL_MODE |

1: Signle channel operation. Operate the DMD array with only Aurora channel 0. 0: Normal operation. Operate the DMD array with all four Aurora channels. |

| gt0_s_axi_user_k_tx_tdata[191:31] | reserved, unused. |

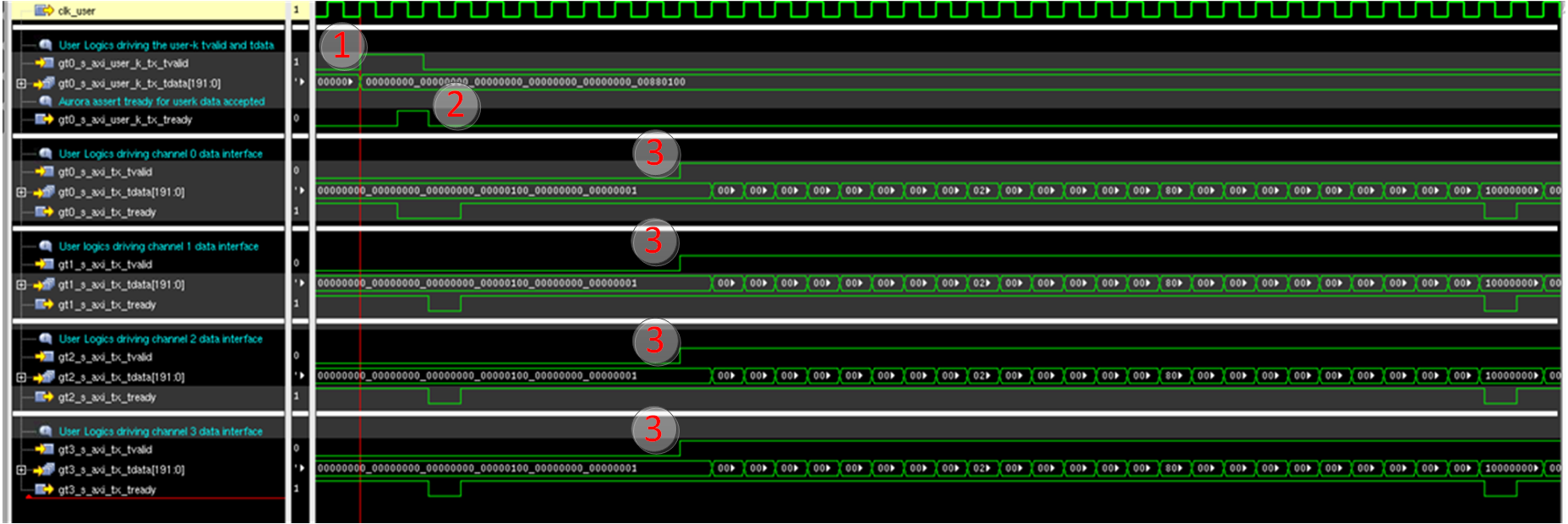

Figure 4-18 showing the transmission of the 192 bits Block Control word over the channel 0 user-k port at the start of an Aurora block transfer (in this example, loading all 136 lines of DMD block 1).

Figure 4-18 Block Start with Block Control

Word Waveform

Figure 4-18 Block Start with Block Control

Word Waveform- With the proper Block Control word on bus gt0_s_axi_user_k_tx_tdata[191:0], the Apps FPGA user logics asserts the TVALID flag (gt0_s_axi_user_k_tx_tvalid), and waits for the response of the Aurora core.

- Aurora asserts the TREADY flag, gt0_s_axi_user_k_tx_tready, indicating the core has accepted the 192 bits user-k data.

- After the Block Control word is sent, Apps FPGA user logic starts the Aurora block transfer on all four data interfaces.