SBAA491A November 2021 – April 2022 PCM5120-Q1 , PCM6120-Q1 , TLV320ADC5120 , TLV320ADC6120

2 Dynamic Range Enhancer

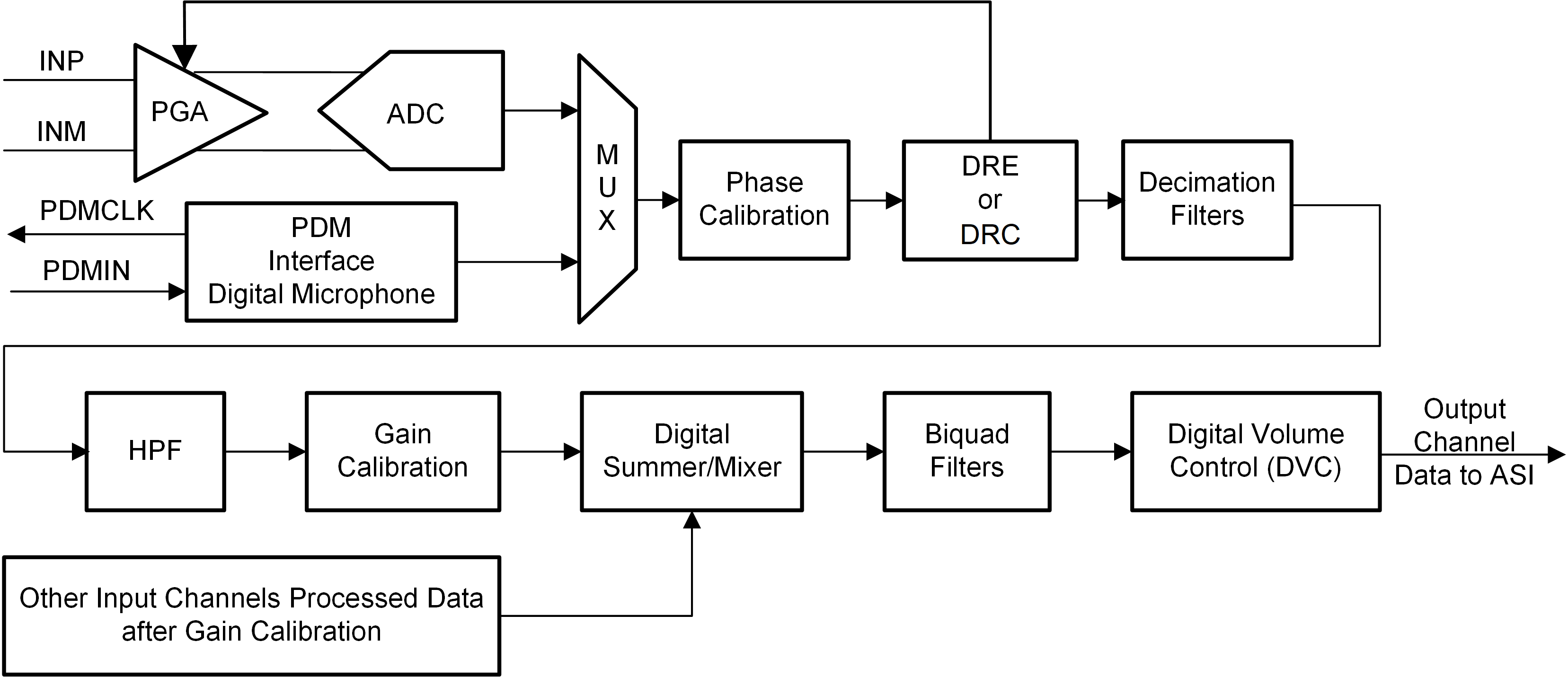

Figure 2-1 shows the signal processing chain for TLV320ADC5120/PCM5120-Q1 and TLV320ADC6120/PCM6120-Q1 devices. The dynamic range performance of the front-end PGA in TLV320ADC5120/PCM5120-Q1 and TLV320ADC6120/PCM6120-Q1 devices are 120 dB and 122 dB respectively. The subsequent delta-sigma ADC has 108 dB dynamic range for the TLV320ADC5120 /PCM3120-Q1 and 113 dB dynamic range for the TLV320ADC6120/PCM6120-Q1 .Without the DRE, the ultra-low noise performance of the PGA is limited by the ADC performance and the overall channel dynamic range is determined by the dynamic range of the ADC. With the DRE, the overall channel dynamic range can be improved beyond the dynamic range of the ADC and is limited more by the dynamic range of the PGA.

Figure 2-1 Signal Processing Block Diagram

Figure 2-1 Signal Processing Block DiagramThe DRE algorithm monitors the input signal and increases the gain of the analog PGA for signal levels below a threshold. At the same time, the DRE algorithm creates a corresponding reciprocal attenuation in the digital circuits so the net effect of the analog PGA gain and digital attenuation cancel each other out. Thus the DRE improves the dynamic range without increasing the overall channel gain. The DRE does not gain signals above the threshold. Boosting the low-level signals in analog keeps the input to the ADC significantly above its noise floor and thus prevents the ADC performance from being the limiting factor. Subsequent processing is done using a high-performance, 32-bit, digital signal processor with very low quantization noise, and, therefore, the PGA performance becomes the limiting factor in the overall channel performance. TLV320ADC5120 /PCM5120-Q1 and TLV320ADC6120/PCM6120-Q1 devices support up to four analog input channels. All analog input channels support DRE. The devices support differential or single-ended signals from an analog microphone source or auxiliary line input. The analog microphone inputs support electret condenser and microelectrical-mechanical (MEMS) microphones. Even though the devices also support digital pulse density modulated (PDM) digital microphones, the DRE/DRC does not support the digital channels as the analog gain of the digital microphone cannot be controlled. The TLV320ADCx120/PCMx120-Q1 family of devices also support an automatic gain control (AGC) algorithm on the analog channels to maintain a constant nominal output level. AGC, DRE and DRC algorithms cannot be used simultaneously since all these algorithms control the PGA. DRE or AGC selection is done using AGC_DRE_SEL field of DSP_CFG1 register (page = 0x00, address = 0x6C) as shown inTable 2-1.

| BIT | FIELD | TYPE | RESET | DESCRIPTION |

|---|---|---|---|---|

| 3 | DRE_AGC_SEL | R/W | 0h | DRE or DRE selection when is enabled for any channel. 0d = DRE is selected. 1d = DRE is selected. |