SBAS649B June 2021 – June 2022 DAC12DL3200

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - DC Specifications

- 6.6 Electrical Characteristics - Power Consumption

- 6.7 Electrical Characteristics - AC Specifications

- 6.8 Timing Requirements

- 6.9 Switching Characteristics

- 6.10 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 DAC Output Modes

- 7.3.2 DAC Output Interface

- 7.3.3 LVDS Interface

- 7.3.4 Multi-Device Synchronization (SYSREF+/-)

- 7.3.5 Alarms

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

7.3.2.2 Full-scale Current Adjustment

The total DAC output current is set through the external RBIAS resistor and the COARSE_CUR_A/B and the FINE_CUR_A and FINE_CUR_B registers. There is a switched fullscale current and a static fullscale current. The switched current is divided between VOUTA/B+ and VOUTA/B- in proportion to the digital signal value at the DAC. The static current is fixed at the output of each ball VOUTA/B+ and VOUTA/B-.

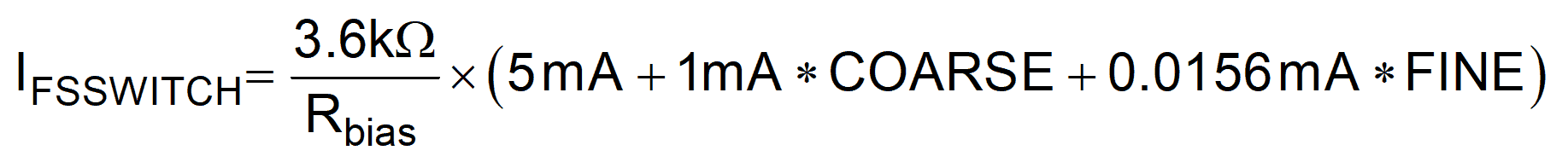

The equation for the total DAC switched output current is

where

- Rbias is the external bias resistor

- COARSE is the value of the register COARSE_CUR_A/B (0 to 15)

- FINE is the value of register FINE_CUR_A/FINE_CUR_B (0 to 63)

The static current is a fixed fraction of the switched current

With a 3.6kΩ bias resistor, COARSE_CUR_A/B = 15 and FINE_CUR_A/B = 31, IFSSWITCHED is nominaly 20.5mA and IFSSTATIC nominally 2.56mA (on each ball + and -).