SCPA063 March 2023 PCA9306

3.6 Are Rise Times Within I2C Standard?

Rise time in I2C is defined as the time taken for the I2C signal to transition from a logic low to a logic high. The minimum value for a logic high in the I2C standard is defined as 70% of VCC; the maximum value for a logic low in the I2C standard is defined as 30% of VCC. Therefore, measure rise time as the time for the I2C signal to transition from 30% of VCC to 70% of VCC. Figure 3-5 shows an example of SDA, SCL during the rise transition. Use an oscilloscope to measure rise times for both the SDA and SCL lines on the I2C bus.

Figure 3-5 Example of Rise Time

Figure 3-5 Example of Rise TimeWhen debugging an I2C bus, verifying that the rise time does not exceed the maximum rise time requirement for the frequency that the I2C bus is operating at (see the table in Figure 3-5) is important. Rise times over the limits outlined by the I2C standards can cause bits of data to be unintentionally removed from a data transfer frame (for each ACK bit from the target, there should be 8 bits sent from the controller). Bus capacitance and pullup resistance are both factors that can affect rise times, so check these two parameters whenever you run into issues with your rise times being over the allowed limits (see the I2C Bus Pullup Resistor Calculation application note for more information on how pullup resistance and capacitance can be used to calculate rise times).

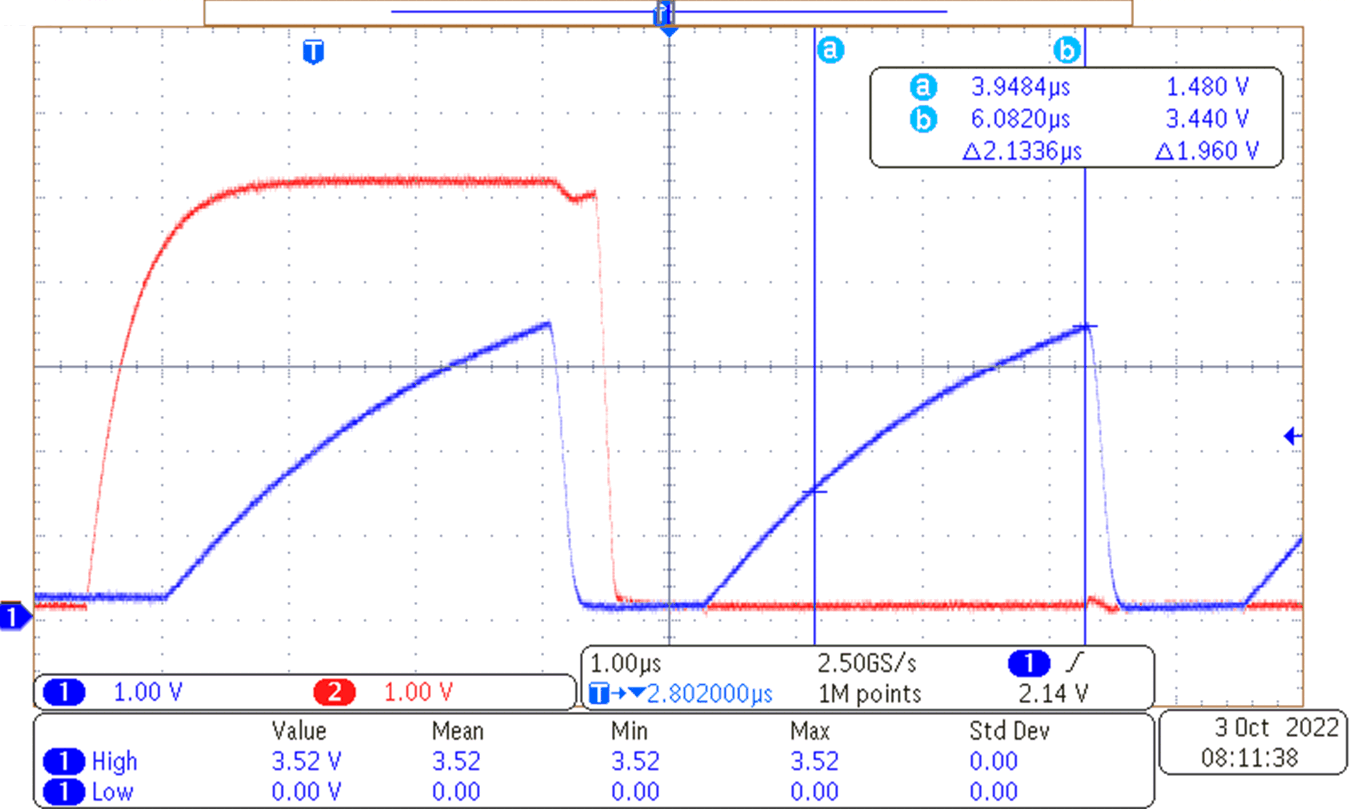

Figure 3-6 shows an example where the rise time exceeds the maximum specified by the I2C standard.

Figure 3-6 Out-of-Specification Rise Time Example

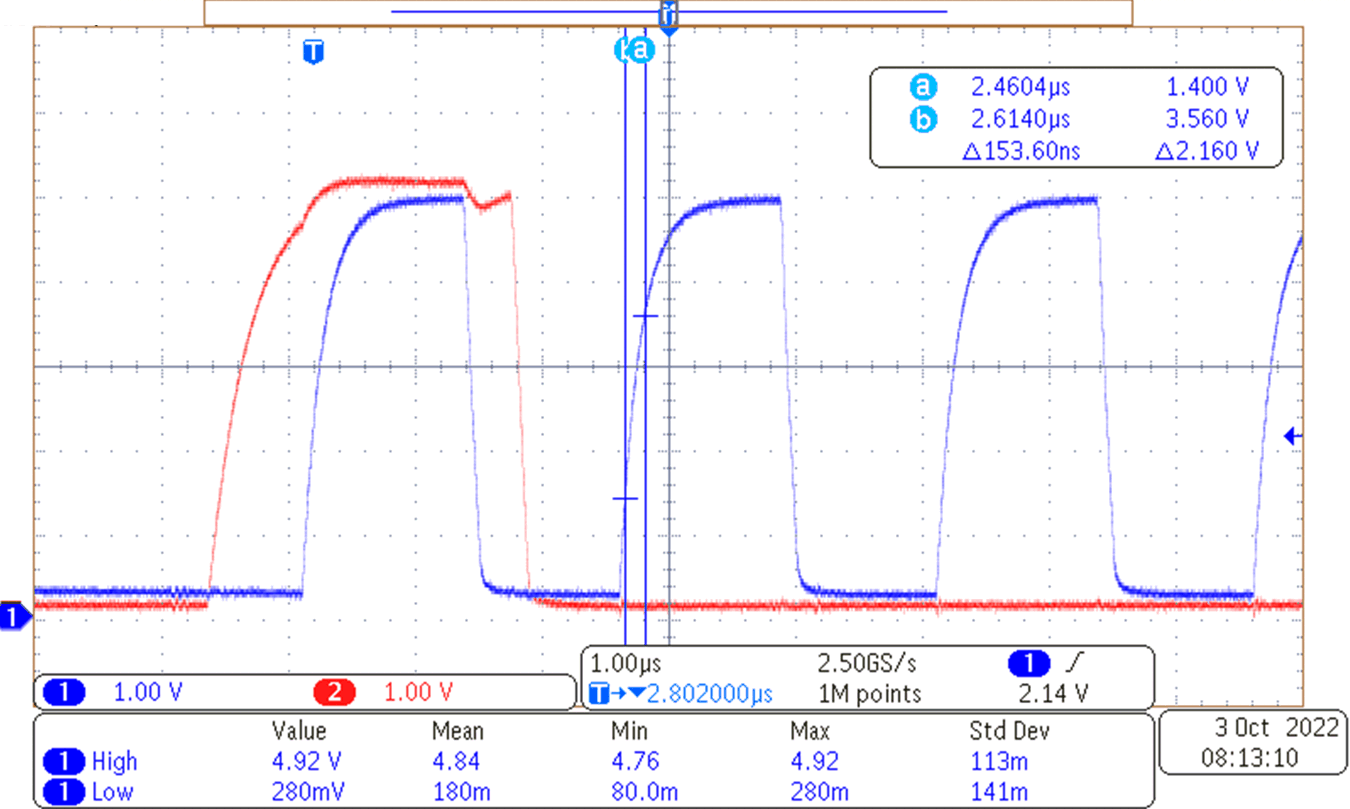

Figure 3-6 Out-of-Specification Rise Time ExampleFigure 3-7 shows an example where the rise time is compliant with the I2C standard.

Figure 3-7 Rise Time Within Specification Example

Figure 3-7 Rise Time Within Specification Example