SCPA063 March 2023 PCA9306

3.7 Are the Sent Command Bytes Valid?

If a command byte is not defined for a particular target device, a NACK is sent to the controller. To make sure that the correct command byte for a device is sent, use an oscilloscope to check if all of the 8 bits sent to the target match the bits of the command defined in the data sheet of the device. Remember that the command byte needs to be sent after the address byte and before the data byte in a frame.

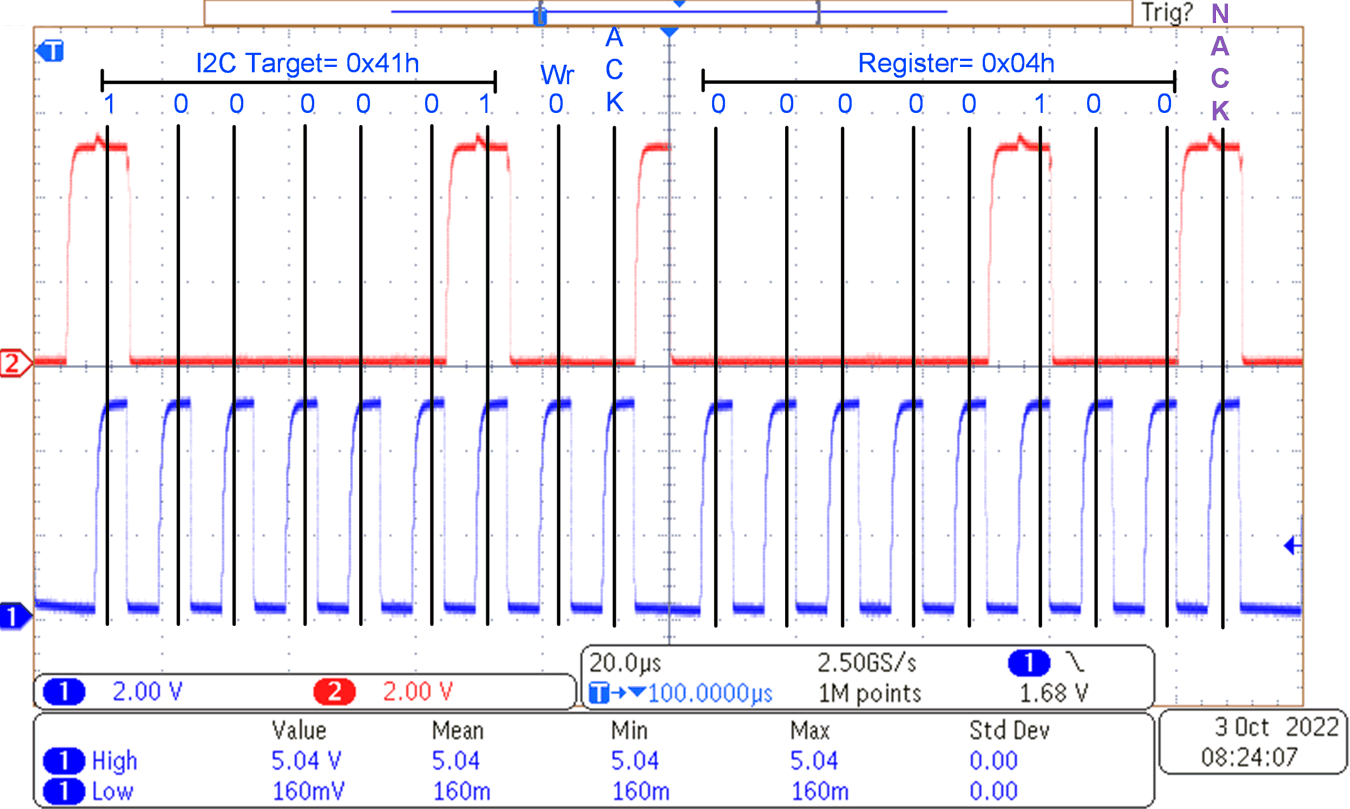

Figure 3-9 shows an example where the I2C target address and write bit is sent followed by a bad (outside of the available registers of the I2C target) command byte resulting in a NACK. The target device in this example only has four registers (0x00h to 0x03h). If a command byte with the register value of 0x04h is sent, the result expected is a NACK, since 0x04h is outside of the acceptable bytes of 0x00h to 0x03h.

Figure 3-8 Example of Invalid Register

Receiving a NACK

Figure 3-8 Example of Invalid Register

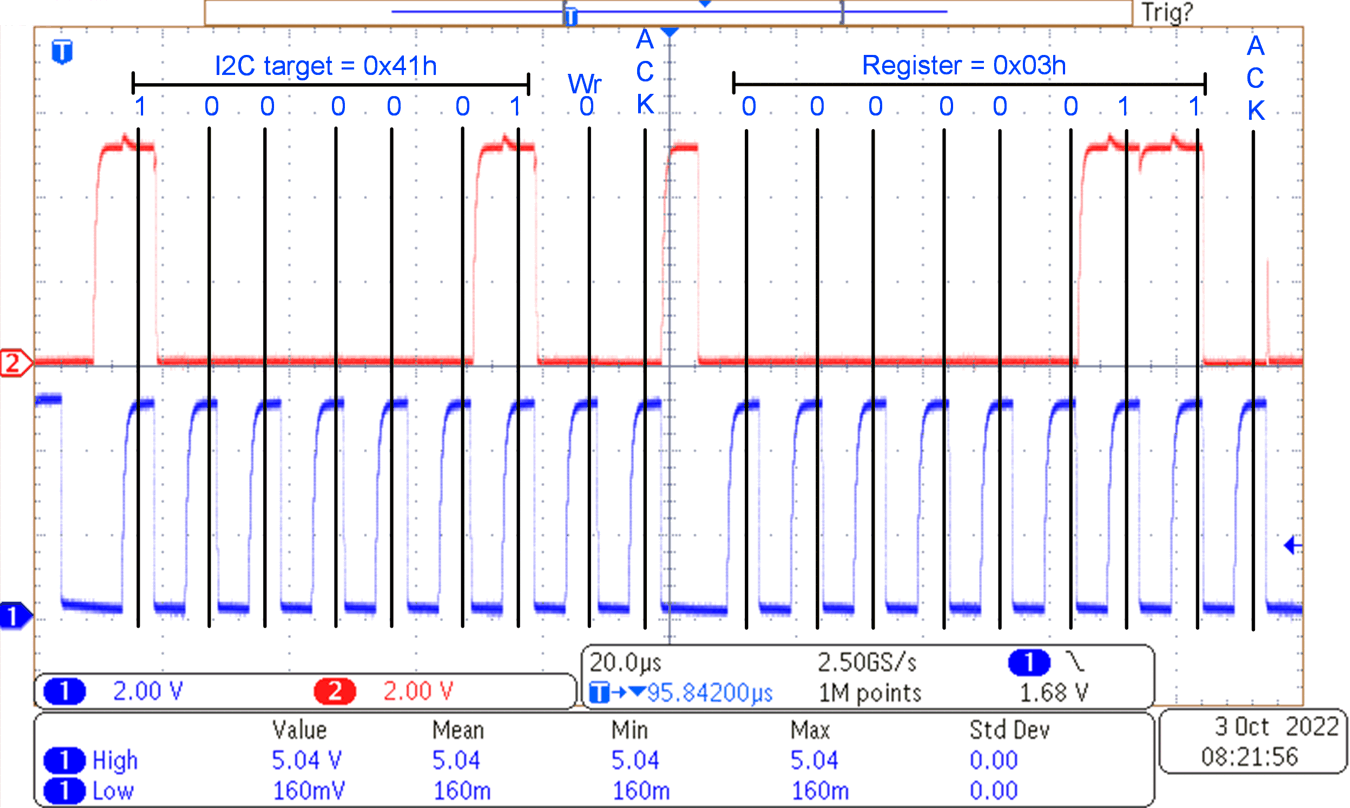

Receiving a NACKFigure 3-9 shows an example using the same I2C target address and write bit from Figure 3-8 but a known good command byte (a command byte recognized by the I2C target) is sent resulting in an ACK. The target device in this example accepts the 0x03h register byte because the target device has a register between values of 0x00h and 0x03h, all of which are registers that can be written to.

Figure 3-9 Example of Acceptable Command

Byte Receiving an ACK

Figure 3-9 Example of Acceptable Command

Byte Receiving an ACK