SLVA857B July 2018 – January 2023 TPS50601-SP , TPS50601A-SP , TPS7H1101-SP , TPS7H1101A-SP , TPS7H3301-SP , TPS7H4001-SP

2 RTG4 Power-Up and Power-Down Requirements

The power-up requirements are based on the VDDPLL and the SERDES_x_Lyz_VDDAIO voltage rails. The only way to not have any power-up sequencing requirements are to hold the RTG4 in reset (by asserting DEVRST_N) until the VDDPLL supply reaches its minimum recommended level and to have the SERDES_x_Lyz_VDDAIO supplies tied to VDD. If this cannot be done however, then the RTG4 voltage rails need to be properly sequenced. In this case, the following requirements apply:

- VDDPLL must not be the last supply to ramp up and must reach its minimum recommended level before the last supply (VDD or VDDIx) starts ramping up.

- VDD core and SERDES IO must be powered up in parallel.

There is no power-down requirement if an external 1-kΩ pull-down resistor is used for each critical output that cannot tolerate an output glitch during power-down or DEVRST_N assertion.

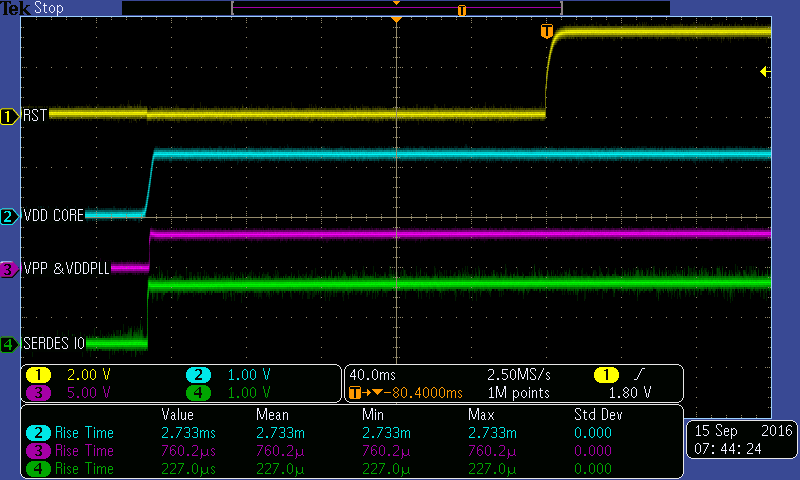

Microsemi has a development kit intended to demonstrate the capabilities of the RTG4 and expedite software development. The power distribution for this development board is shown in Figure 2-1. In this design, Microsemi uses a reset supervisor that holds the FPGA in reset for approximately 150 ms after the 3.3-V, 10-A regulator comes up. This allows sufficient time for all rails to reach regulation before the device begins operation bypassing the need for a power-up sequence. The oscilloscope plot in Figure 2-2 shows the main rails on startup while the device is held in reset. All of the voltage rails come up at the same time and reach their recommended operating points before the reset supervisor releases the active low reset.

Figure 2-1 RTG4 Development Board Power

Distribution

Figure 2-1 RTG4 Development Board Power

Distribution Figure 2-2 RTG4 Development Board

Start-up Sequence

Figure 2-2 RTG4 Development Board

Start-up Sequence