SNAU252 June 2020 LMK04832-SP

- LMK04832EVM-CVAL User’s Guide

- A TICS Pro Usage

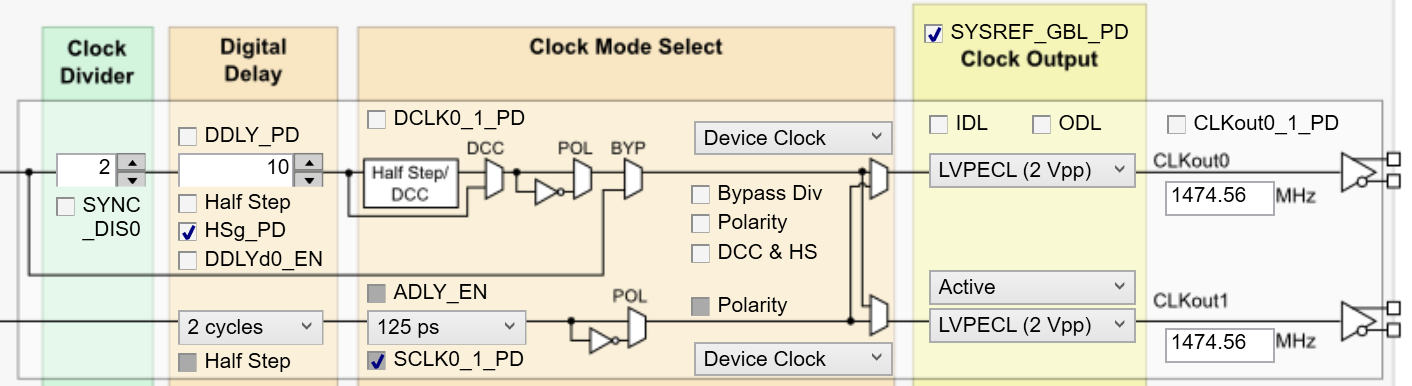

5.6 Enable Clock Outputs

The LMK04832-SP offers programmable clock output buffer formats, the evaluation board is shipped with pre-configured output terminations. Refer to Table 5 to see a list of the outputs what the output format the hardware is configured for out of the factory.

To measure Phase noise at one of the clock outputs, for example CLKout0:

- Click on the Clock Outputs page, Section A.9

- Uncheck CLKoutX_Y_PD in the Clock Output box to enable the channel,

- Set the following as needed:

- For Device Clock:

- DCLKX_Y_PD = 0 in Clock Mode Select box.

- Set Bypass Div (DCLKX_Y_BYP) or Clock Divider (DCLK0_1_DIV) as desired for device clock frequency.

- If bypass mode is set, CLKoutX must be set to a CML output format. Bypass mode is not available on CLKoutY.

- If Clock Divider = 1, then DCLKX_Y_DCC must be set for clock output.

- Phase of the device clock can be adjusted with:

- Static Digital delay (DCLKX_Y_DDLY) after a SYNC. Digital Delay (DCLKX_Y_DDLY_PD) must be powered up.

- Dynamic Digital delay (DDLYdX_EN), then programming DDLYd_STEP_CNT. Digital Delay (DCLKX_Y_DDLY_PD) must be powered up. Press the Send button at top right of Clock Outputs window to program the DDLYd_STEP_CNT field multiple times.

- Half Step bit (DCLKX_Y_HS) if DCC & HS (DCLKX_Y_DCC) is set.

- The Polarity bit (DCLKX_Y_POL)

- Select the Device Clock for CLKoutX or CLKoutY with CLKout#_SRC_MUX = 0 (Device Clock) as desired.

- While the phase noise of a SYSREF Clock is typically not of concern, to configure an output for SYSREF:

- SCLKX_Y_PD = 0 in Clock Mode Select box.

- Phase of the SYSREF clock can be adjusted.

- Local digital delay can be set with SCLKX_Y_DDLY.

- Local analog delay can be set by enabling with ADLY_EN = 1 (SCLKX_Y_ADLY_EN) and then setting SCLKX_Y_ADLY to the desired time delay.

- Global digital delay can be set with SYSREF_DDLY, but this delay change will take effect only after a SYNC.

- Globally SYSREF output must be enabled. The necessary bits depend upon the type of SYSREF to be enabled. For a simple continuous SYSREF (not recommended in final application due to extra power consumption and crosstalk), set SYSREF_PD = 0, SYSREF_MUX = 0x03 (Continuous), and SYNC_DISSYSREF = 1.

- Select the SYSREF clock for CLKoutX or CLKoutY with CLKout#_SRC_MUX = 1 (SYSREF) as desired.

- For Device Clock:

- Depending on the configured output type, the clock output SMAs can be interfaced to a test instrument with a single-ended, 50-Ω input as follows.

- For LVDS:

- A balun (like ADT2-1T or high quality Prodyn BIB-100G) is recommended for differential-to-single-ended conversion.

- For LVPECL:

- A balun can be used, or

- One side of the LVPECL signal can be terminated with a 50-Ω load and the other side can be run single-ended to the instrument.

- For HSDS:

- A balun (like ADT2-1T or high-quality Prodyn BIB-100G) is recommended for differential-to-single-ended conversion.

- For CML:

- A balun can be used, or

- One side of the CML signal can be terminated with a 50-Ω load and the other side can be run single-ended to the instrument.

- For LVCMOS:

- Connect the LVCMOS signal to measurement equipment as desired. If an output of a pair is not used, TI recommends leaving the output floating close to the IC. Alternatively, place a 50-Ω termination at the end of an unused trace.

- For LVDS:

- The phase noise may be measured with a spectrum analyzer or signal source analyzer.

Figure 7. Setting Digital Delay, Clock Divider, Analog Delay, and Output Format

Figure 7. Setting Digital Delay, Clock Divider, Analog Delay, and Output Format