SNAU260A October 2020 – February 2021 LMK5C33216

ADVANCE INFORMATION

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM Schematics

- 4.1 Power Supply Schematic

- 4.2 Power Distribution Schematic

- 4.3 LMK5C33216 and Input Reference Inputs IN0 to IN1 Schematic

- 4.4 Clock Outputs OUT0 to OUT3 Schematic

- 4.5 Clock Outputs OUT4 to OUT9 Schematic

- 4.6 Clock Outputs OUT10 to OUT15 Schematic

- 4.7 XO Schematic

- 4.8 Logic I/O Interfaces Schematic

- 4.9 USB2ANY Schematic

- 5EVM Bill of Materials

- 6Appendix A - TICS Pro LMK5C33216 Software

- 7Revision History

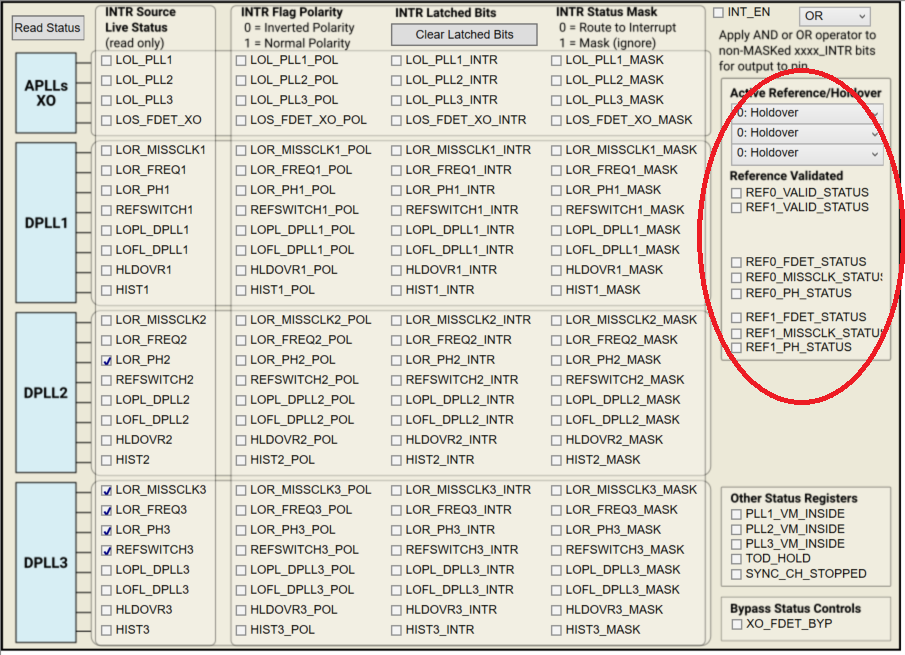

6.2 Using the Status Page

The status page shows fields pertaining to the current status of the device. The update these fields click the Read Status Bits button or the Read RO Regs button in the tool bar. The Read RO Regs button will read all read only registers which provides more information on other pages including the status fields but can take longer to read back. The read status bits just reads the status bits for this page.

For the DPLL to lock, a reference must be validated and selected as shown in the Active Reference/Holdover and Reference Validated portion of the window, as seen in the circled portion of Figure 6-7.

As the DPLL locks, it is expected to see the LOPL_DPLLx as the last bit to become clear when the phase lock is acquired.

When INT_EN = 1, any live status flag which occurs will latch to the INTR Latched bit columns. These will remain asserted until the Clear Latched Bits button is selected. This gives additional insight into the behavior of the device.

Pressing the Soft-chip reset button in the toolbar will cause the device to reset and re-start lock.

Figure 6-7 Status

Page

Figure 6-7 Status

Page