SNLA308A April 2019 – October 2020 DS90UB941AS-Q1 , DS90UH941AS-Q1

- Trademarks

- 1 Introduction

- 2 Superframe Requirements

- 3 Video Processing Status Monitoring

- 4 Superframe Splitting

-

5 Frame Cropping

- 5.1

Cropping Control Registers

- 5.1.1 CROP_START_X0_CROP_START_X0_P1 Register (Address = 36h) [reset = 0h]

- 5.1.2 CROP_START_X1_CROP_START_X1_P1 Register (Address = 37h) [reset = 0h]

- 5.1.3 CROP_STOP_X0_CROP_STOP_X0_P1 Register (Address = 38h) [reset = 0h]

- 5.1.4 CROP_STOP_X1_CROP_STOP_X1_P1 Register (Address = 39h) [reset = 0h]

- 5.1.5 CROP_START_Y0_CROP_START_Y0_P1 Register (Address = 3Ah) [reset = 0h]

- 5.1.6 CROP_START_Y1_CROP_START_Y1_P1 Register (Address = 3Bh) [reset = 0h]

- 5.1.7 CROP_STOP_Y0_CROP_STOP_Y0_P1 Register (Address = 3Ch) [reset = 0h]

- 5.1.8 CROP_STOP_Y1_CROP_STOP_Y1_P1 Register (Address = 3Dh) [reset = 0h]

- 5.2 Cropping Options

- 5.1

Cropping Control Registers

- 6 Splitter Mode Pixel Clocks

- 7 Programming Example

- 8 Summary

- 9 References

- 10Handling Interrupts With the DS90Ux941AS-Q1

-

11High-Speed GPIO Operation in Splitter Mode

- 11.1 Introduction

- 11.2 High-Speed Control Configuration

- 11.3 Back Channel Frequency Configuration

- 11.4 Splitter Mode GPIO

- 11.5 GPIO_0_Config Register (Address = Dh) [reset = 20h]

- 11.6 GPIO_1_and_GPIO_2_Config Register (Address = Eh) [reset = 0h]

- 11.7 GPIO_3_Config Register (Address = Fh) [reset = 0h]

- Revision History

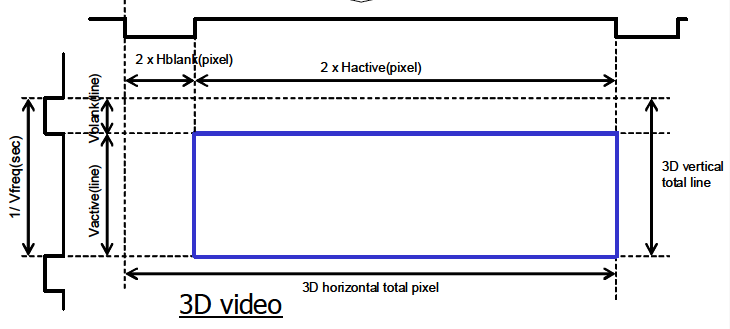

2.3 Alternate Pixel 3D Format

The DS90Ux941AS-Q1 formats a superframe as a dual-image with alternating pixels. The DS90Ux941AS-Q1 does not require any special processing on this image format. This superframe can be split by the DS90Ux941AS-Q1 and sent to two independent deserializers.

The following are requirements for proper operation:

- Images must have identical video format (lines, pixels, blanking intervals).

- Pixel clock used must be twice the frequency as required for sending a single image.

- Horizontal blanking components (front porch, sync period, back porch) must be twice the number of pixels as required for a single image.

- Vertical blanking periods must be the same number as required for a single image. Note that the total time spent on vertical blanking in the dual image is twice that of the time spent in the single image, as the vertical blanking happens for two times the number of lines in a single image.

- The maximum line size allowed is 4095 pixels (24-bit).

Figure 2-3 HDMI 1.4b Alternate Pixel 3D Format

Figure 2-3 HDMI 1.4b Alternate Pixel 3D FormatAlternate Pixel mode is the default mode of operation for the DS90Ux941AS-Q1.

If splitter mode is enabled, there are two options to properly regenerate Horizontal Sync timing. The preferred option is to use the default setting for the IMG_DELAY, and enable a register override of the Horizontal Sync and Horizontal Back porch periods for each port using the IMG_HSYNC_CTLx registers. Front Porch value may be determined from total line length - (Active line length + Horizontal Back Porch + Horizontal Sync). The second option is to allow automatic generation of the Horizontal Sync timing and set the IMG_DELAY value in registers 0x34 0x35 to greater than the Horizontal Sync period plus the Horizontal Back Porch period for the 3D image in pixels.