SWRA689 February 2022 AWR6843 , AWR6843AOP , IWR6843 , IWR6843AOP

- Trademarks

- 1Introduction

- 2Radar System Overview

- 3Active Mode Optimizations

- 4Idle Mode Optimizations

- 5Power Measurement Methods and Results

- 6References

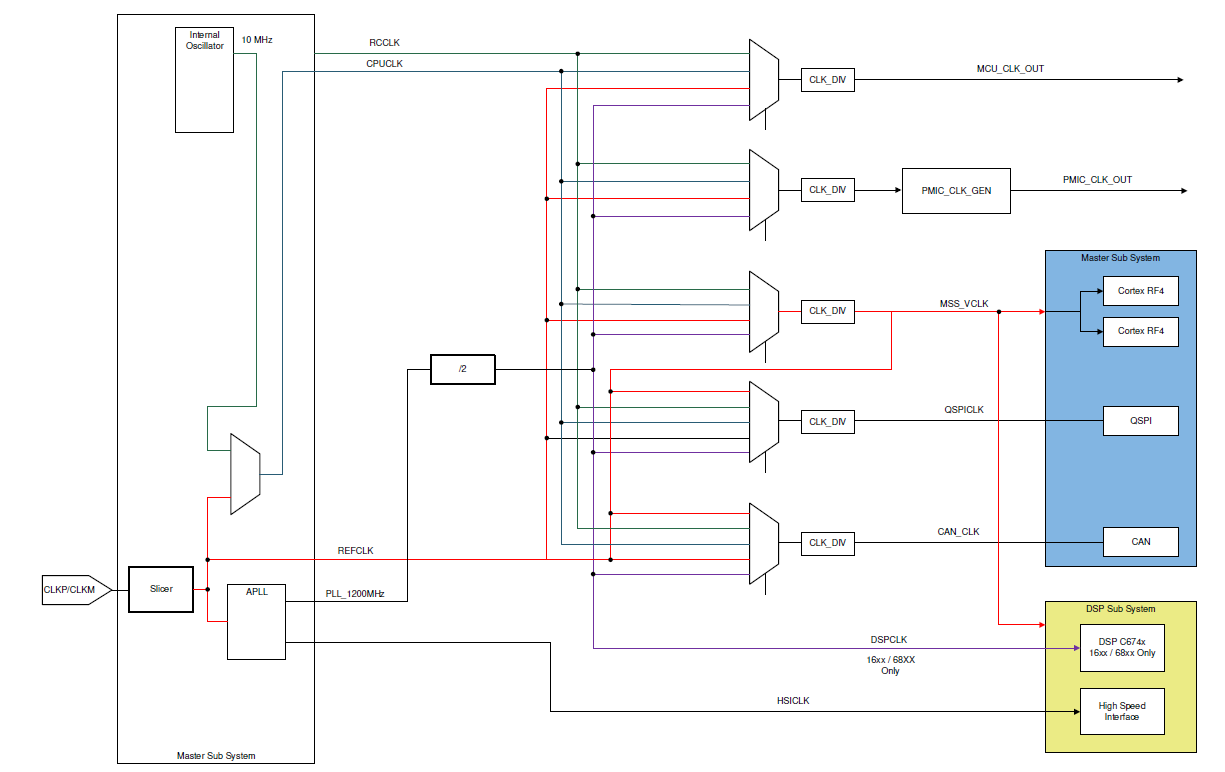

4.2.2 Digital Domain Components

Figure 4-2 Digital Domain Components

Figure 4-2 Digital Domain Components