TIDUF65 March 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing Requirements, and Test Results

- 5Performance Comparison with Competitor’s Device

- 6Design and Documentation Support

- 7About the Author

4.4.5 Adjacent Current Rejection

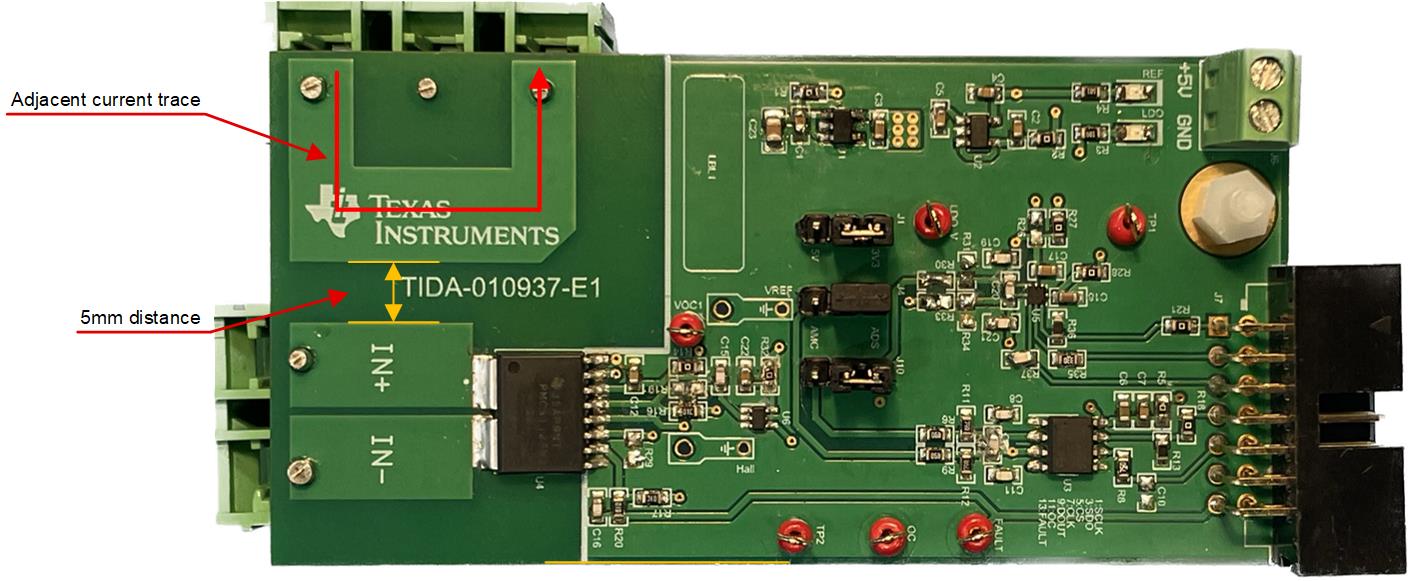

For the adjacent current rejection test, the test setup is similar with OC response test. Please refer to Section 4.4.4 for details. The only difference is that the 40A current pulse is injected to the adjacent trace shown in Figure 4-22 to simulate the magnetic field interference.

Figure 4-22 Adjacent Current Trace

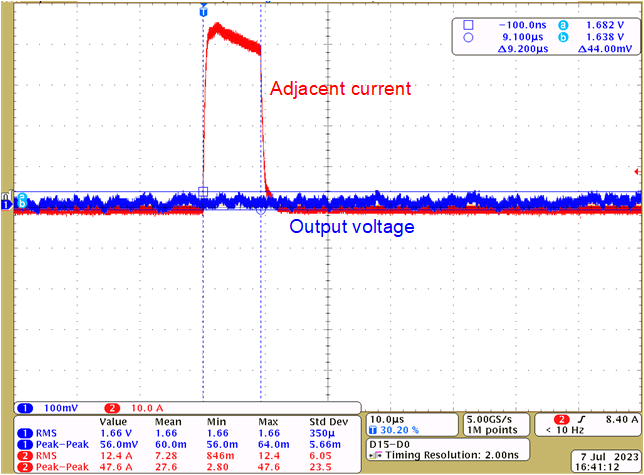

Figure 4-22 Adjacent Current TraceFrom Figure 4-23, the 40A peak input adjacent current has no influence on the output voltage. There is no significant disturbance on output voltage at the adjacent current rising and falling edge. The output voltage is dominated by the output noise of the TMCS1123.

Figure 4-23 Adjacent Current and Output

Voltage

Figure 4-23 Adjacent Current and Output

Voltage