SBAS650C May 2014 – April 2021 AFE4403

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Family Options

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application Information Disclaimer

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YZP|36

Thermal pad, mechanical data (Package|Pins)

Orderable Information

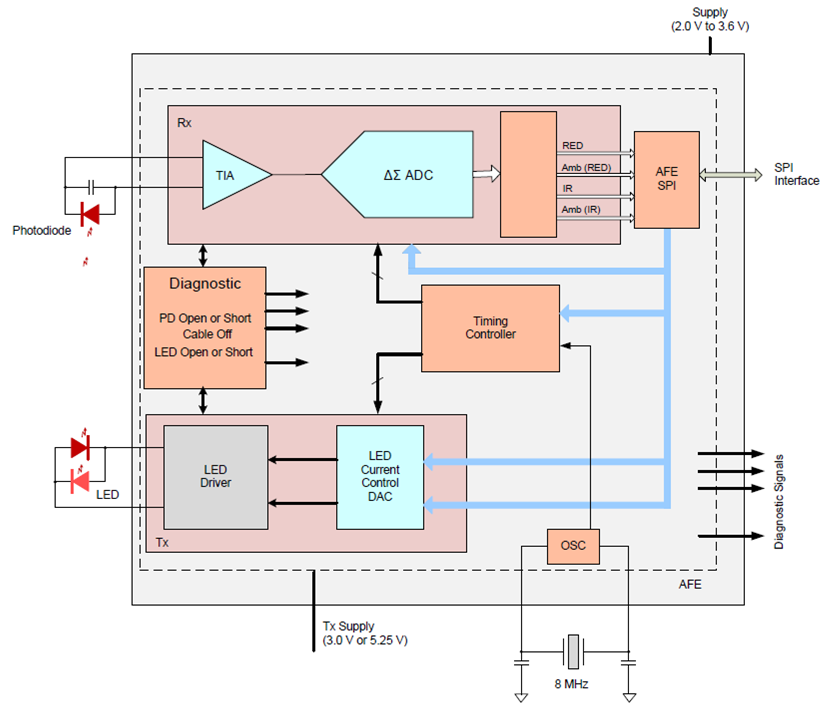

3 Description

The AFE4403 is a fully-integrated analog front-end (AFE) ideally suited for pulse oximeter applications. The device consists of a low-noise receiver channel with an integrated analog-to-digital converter (ADC), an LED transmit section, and diagnostics for sensor and LED fault detection. The device is a very configurable timing controller. This flexibility enables the user to have complete control of the device timing characteristics. To ease clocking requirements and provide a low-jitter clock to the AFE4403, an oscillator is also integrated that functions from an external crystal. The device communicates to an external microcontroller or host processor using an SPI™ interface.

The device is a complete AFE solution packaged in a single, compact DSBGA-36 (3.07 mm × 3.07 mm × 0.5 mm) and is specified over the operating temperature range of –20°C to 70°C.

| PART NUMBER | PACKAGE(1) | BODY SIZE (NOM) |

|---|---|---|

| AFE4403 | DSBGA (36) | 3.07 mm × 3.07 mm |

Block Diagram

Block Diagram