TIDUCL0 January 2017

- 1 Description

- 2 Resources

- 3 Features

- 4 Applications

- 5 Design Images

- 6 System Overview

-

7 System Design Theory

- 7.1 Power Stage Design—Battery Power Input to the Board

- 7.2 Power Stage Design—Three-Phase Inverter

- 7.3 Power Stage Design—DRV8323 Gate Driver

- 7.4 Power Stage Design—18-V to 3.3-V DC-DC Converter

- 7.5 Power Stage Design —Microcontroller MSP430

- 7.6 Power Stage Design—Hall Sensor Interface

- 7.7 Temperature Sensing

- 7.8 Power Stage Design—External Interface Options and Indications

- 8 Getting Started Hardware and Software

- 9 Testing and Results

- 10Design Files

- 11Software Files

- 12Related Documentation

- 13Terminology

- 14About the Author

9.2.6.2 Stall Current Latch Protection by DRV8323 VDS Sensing

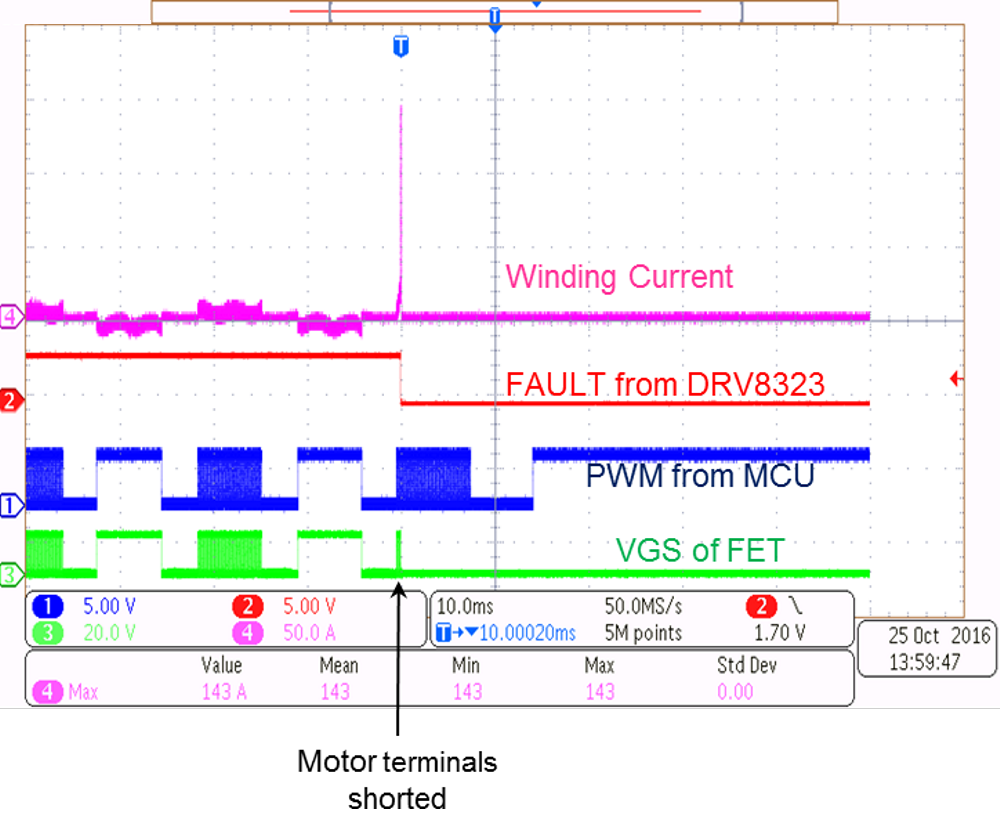

The same test setup in Figure 45 is used for the stall current protection. The VDS reference used is 0.1 by writing in the register of the DRV8323. The latch protection acted at 143 A.

Figure 50 shows the test results with latch protection by VDS sensing. When a VDS overcurrent event occurs, the device will pull all gate drive outputs low to put all six external MOSFETs into high impedance mode. The fault will be reported on the nFAULT pin with the specific MOSFET in which the overcurrent event was detected is reported through the SPI status registers. Figure 51 shows the zoomed view of Figure 50.

Figure 50. Overcurrent Latch Protection With Motor Stall by VDS Sensing

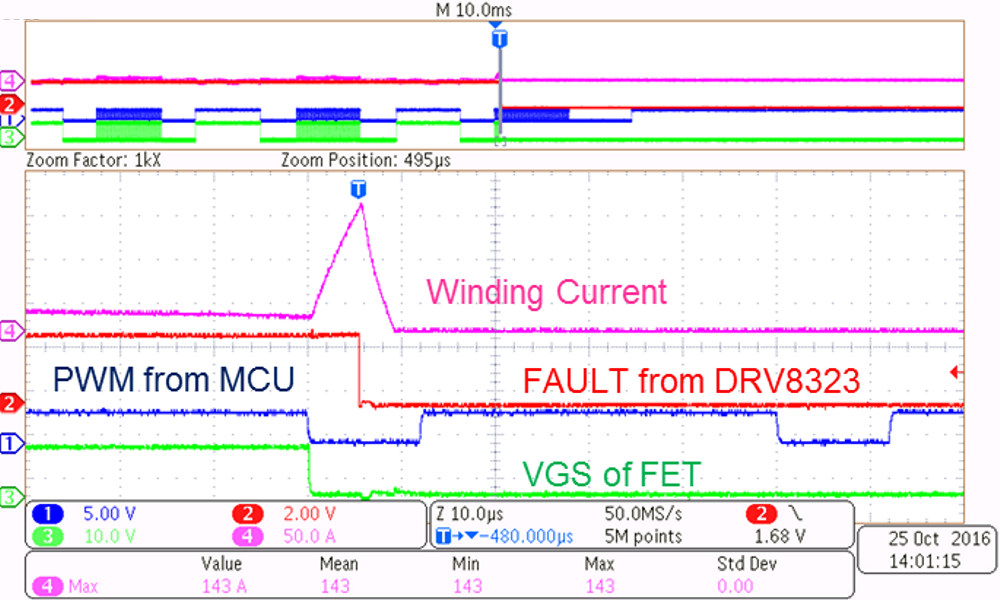

Figure 50. Overcurrent Latch Protection With Motor Stall by VDS Sensing  Figure 51. Zoomed View of Overcurrent Latch Protection With Motor Stall by VDS Sensing

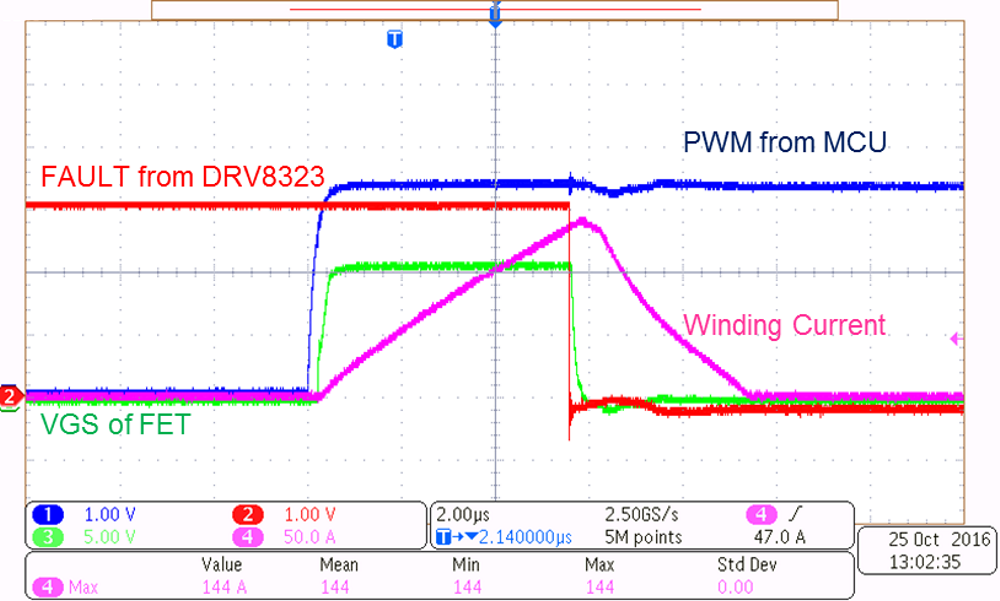

Figure 51. Zoomed View of Overcurrent Latch Protection With Motor Stall by VDS Sensing Figure 52 shows the test results of latch protection, when the inverter output is shorted. The same test setup in Figure 48 is used for the short-circuit simulation. The VDS reference used is 0.1 V. The latch protection acted at 144 A.

Figure 52. Overcurrent Latch Protection With Inverter Output Shorted

Figure 52. Overcurrent Latch Protection With Inverter Output Shorted