SPRADA3 july 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Device Nomenclature

- 3 R5 Cores and TCM in AM263x

- 4 Example Support for AM263x Family

- 5 IPC Example Support for Two-Core Devices (AM2632)

- 6 System Project Example Support for Two-Core Devices (AM2632)

- 7 Target Configuration in CCS

- 8 Connecting to the Target Core

- 9 Hardware Description for Launch Pad and Control Card

- 10Summary

- 11References

5.1 Option 1 Using MulticoreImageGen.js

This section provides a simple method to create a Dual Lockstep Core (two cores) example from an existing four-core IPC Notify example. This example does not involve any system project; therefore, the user must use the command line to create a final combined app image. Steps for creating a Dual Core Appimage are described below.

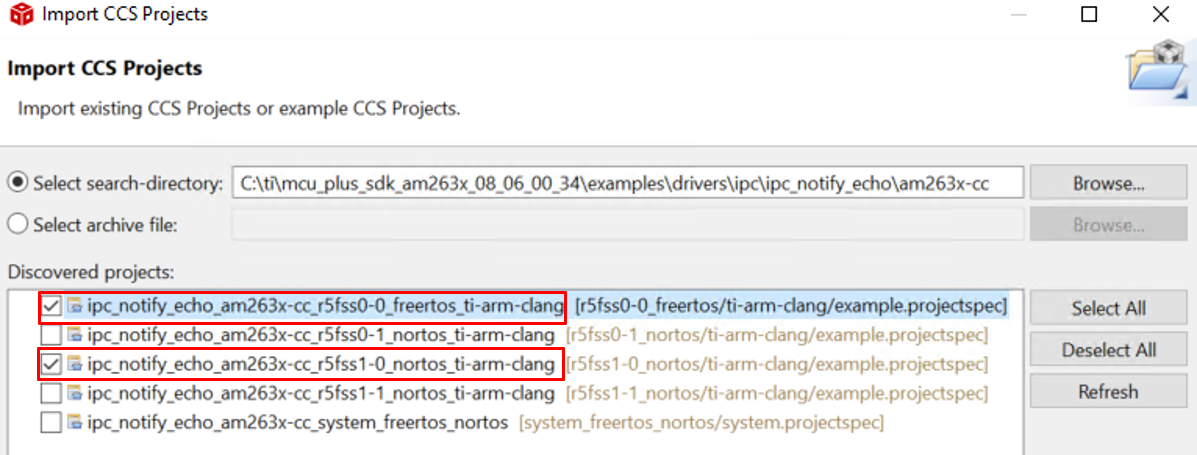

- Import IPC Notify example for R50-0 and R51-0 (see also Section 3.1) from the SDK as shown below. Ignore the system project.

Figure 5-1 IPC Notify Example for R50-0 and R51-0

Figure 5-1 IPC Notify Example for R50-0 and R51-0- Modify your example.syscfg to support the IPC notify feature to the cores 0-0 and 1-0. Subsequently, disable IPC Notify feature for cores 1-0 and 1-1.

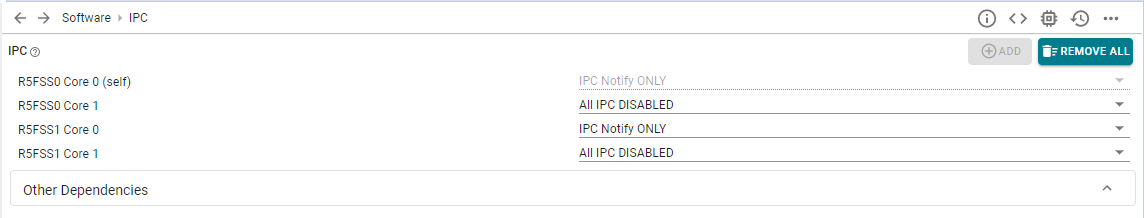

Figure 5-2 IPC Notify R50_0 Syscfg

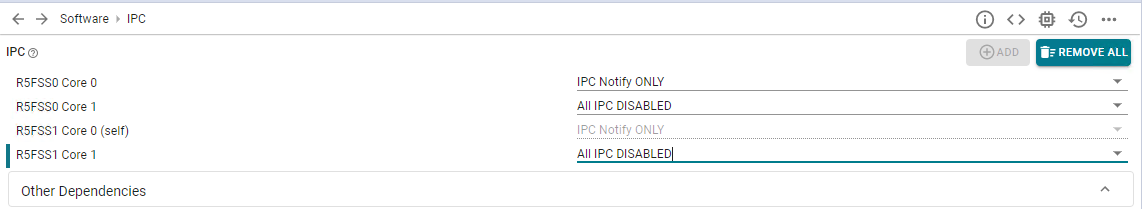

Figure 5-2 IPC Notify R50_0 Syscfg Figure 5-3 IPC Notify R51_0 Syscfg

Figure 5-3 IPC Notify R51_0 Syscfg- Change the Remote Core ID list to support only core 1-0, and remove remaining cores as shown below. Make this change in ipc_notify_echo .c file of both ipc_notify_echo_am263x-cc_r5fss0-0_nortos_ti-arm-clang and ipc_notify_echo_am263x-cc_r5fss1-0_nortos_ti-arm-clang projects.

uint32_t gRemoteCoreId[] = {

CSL_CORE_ID_R5FSS1_0,

CSL_CORE_ID_MAX

};- Build these projects individually. After building, .rprc files are available for both the projects.

- Combine these .rprc to form a dual-core .appimage using the following command.

C:\ti\\{sysconfig}\nodejs\node C:\ti\\{mcu_plus_sdk}/tools/boot/multicoreImageGen/multicoreImageGen.js --devID 55 --out Debug/Combined.debug.appimage ../ipc_notify_echo_am263x-cc_r5fss0-0_freertos_ti-arm-clang/Debug/ipc_notify_echo_am263x-cc_r5fss0-0_freertos_ti-arm-clang.rprc@0 ../ipc_notify_echo_am263x-cc_r5fss1-0_nortos_ti-arm-clang/Debug/ipc_notify_echo_am263x-cc_r5fss1-0_nortos_ti-arm-clang.rprc@2The command format for MulticoreImage Generation is given below.

cd ${SDK_INSTALL_PATH}/tools/boot/multicoreImageGen${NODE} multicoreImageGen.js --devID {DEV_ID} --out {Output image file (.appimage)} {core 1 rprc file}@{core 1 id} [ {core n rprc file}@{core n id} ... ]