TIDUE53I march 2018 – july 2023 TMS320F28P550SJ , TMS320F28P559SJ-Q1

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1 Required Hardware and Software

- 3.2 Testing and Results

- 4Design Files

- 5Trademarks

- 6About the Authors

- 7Revision History

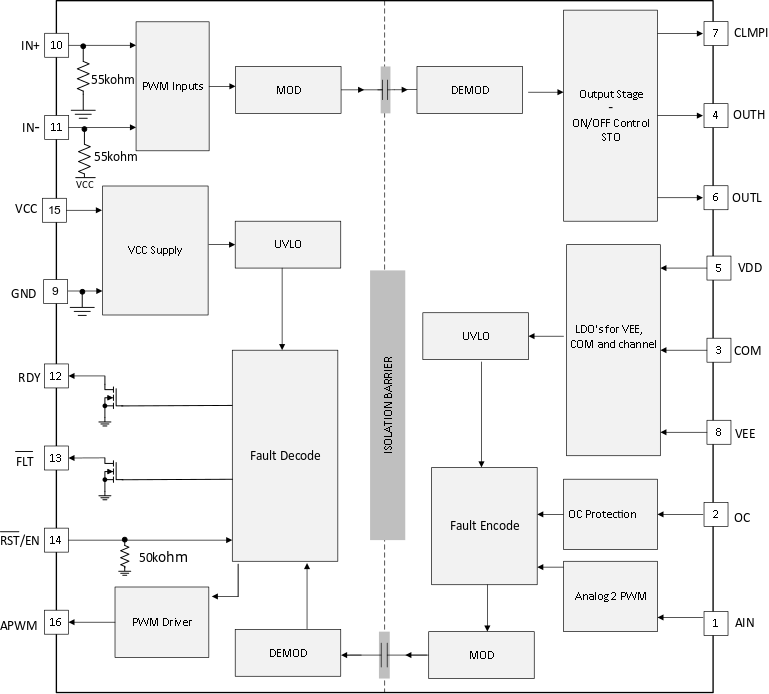

2.2.1 UCC21710

The UCC21710 device is a 5.7-kVRMS, reinforced isolated gate driver for Insulated-Gate Bipolar Transistors (IGBT) and SiC MOSFETs with split outputs, providing 10-A source and 10-A sink current. The input side operates from a single 3-V to 5.5-V supply. The output side allows for a supply range from minimum 13 V to maximum 33 V. Two complementary CMOS inputs control the output state of the gate driver. The short propagation time of 130 ns provides accurate control of the output stage. UCC21710 integrates short circuit protection, detected via Overcurrent detection, with a fast response time needed to protect SiC MOSFETs.

- 150-kV/μs minimum common-mode transient immunity (CMTI)

- Split outputs to provide 10-A peak source and 10-A peak sink currents

- Short propagation delay: 90 ns (typ), 130 ns (max)

- 4-A active Miller clamp

- Output short-circuit clamp

- Soft turn off (STO) during short circuit

- Fault alarm upon desaturation detection is signaled on FLT and reset through RST

- Input and output undervoltage lockout (UVLO) with Ready (RDY) pin indication

- Active output pulldown and default low outputs with low supply or floating inputs

- 2.25-V to 5.5-V input supply voltage

- 15-V to 30-V output driver supply voltage

- CMOS compatible inputs

- Rejects input pulses and noise transients shorter than 40 ns

- Operating temperature: –40°C to +150°C ambient

- Isolation surge withstand voltage of 12800-VPK

Figure 2-2 UCC21710 Functional Block Diagram

Figure 2-2 UCC21710 Functional Block Diagram