DLPS167 March 2024 DLPC964

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4

Device Functional

Modes

- 6.4.1 DLPC964 Aurora 64B/66B Input Data and Command Write Cycle

- 6.4.2 DMD Row Operation

- 6.4.3 Block Load Address Select

- 6.4.4 Block Mode Select

- 6.4.5 Mirror Clocking Pulse (MCP)

- 6.5

Register Map

- 6.5.1

Register Table Overview

- 6.5.1.1 FPGA_INTERRUPT_STATUS Register

- 6.5.1.2 FPGA_INTERRUPT_ENABLE_CONTROL Register

- 6.5.1.3 FPGA_MAIN_STATUS Register

- 6.5.1.4 FPGA_VERSION Register

- 6.5.1.5 FPGA_MAIN_CTRL Register

- 6.5.1.6 SELF_TEST_REG Register

- 6.5.1.7 DMDIF_ERROR_STATUS_CLR Register

- 6.5.1.8 DMDIF_ERROR_STATUS Register

- 6.5.1.9 PRBS7_MACRO0_TEST_RESULT Register

- 6.5.1.10 PRBS7_MACRO1_TEST_RESULT Register

- 6.5.1.11 PRBS7_MACRO2_TEST_RESULT Register

- 6.5.1.12 PRBS7_MACRO3_TEST_RESULT Register

- 6.5.1.13 PRBS7_TEST_CONTROL Register

- 6.5.1.14 PRBS7_TEST_RUNSTATUS Register

- 6.5.1.15 LS_BUS_TEST_RESULT Register

- 6.5.1.16 DMD_TYPE Register

- 6.5.1.17 HSS_RESET Register

- 6.5.1.18 HSS_CHANNEL_STATUS Register

- 6.5.1.19 HSS_LANE_STATUS Register

- 6.5.1.20 HSS_CH0_SOFTERROR_COUNT Register

- 6.5.1.21 HSS_CH1_SOFTERROR_COUNT Register

- 6.5.1.22 HSS_CH2_SOFTERROR_COUNT Register

- 6.5.1.23 HSS_CH3_SOFTERROR_COUNT Register

- 6.5.1.24 HSS_SOFTERROR_COUNT_RESET Register

- 6.5.1.25 HSSI_Channel_0_DMD_Data_GT_Cell_Control Register

- 6.5.1.26 HSSI_Channel_0_DMD_Clock_GT_Cell_Control Register

- 6.5.1.27 HSSI_Channel_1_DMD_Data_GT_Cell_Control Register

- 6.5.1.28 HSSI_Channel_1_DMD_Clock_GT_Cell_Control Register

- 6.5.1.29 HSSI_Channel_2_DMD_Data_GT_Cell_Control Register

- 6.5.1.30 HSSI_Channel_2_DMD_Clock_GT_Cell_Control Register

- 6.5.1.31 HSSI_Channel_3_DMD_Data_GT_Cell_Control Register

- 6.5.1.32 HSSI_Channel_3_DMD_Clock_GT_Cell_Control Register

- 6.5.1.33 HSSI_DMD_Vcm_Value Register

- 6.5.1.34 TEST_DMD_ID Register

- 6.5.1.35 TEST_DMD_FUSE1 Register

- 6.5.1.36 TEST_DMD_FUSE2 Register

- 6.5.1.37 TEST_DMD_FUSE3 Register

- 6.5.1.38 TEST_DMD_FUSE4 Register

- 6.5.1

Register Table Overview

-

7 Application and Implementation

- 7.1 Application Information

- 7.2 Typical Application

- 7.3 Interfacing to DLPC964 Controller High Speed Serial (HSS) Aurora 64B/66B Inputs

- 7.4 Power Supply Recommendations

- 7.5 Layout

- 7.6 Layout Example

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DLP|48

Thermal pad, mechanical data (Package|Pins)

Orderable Information

4 Pin Configuration and Functions

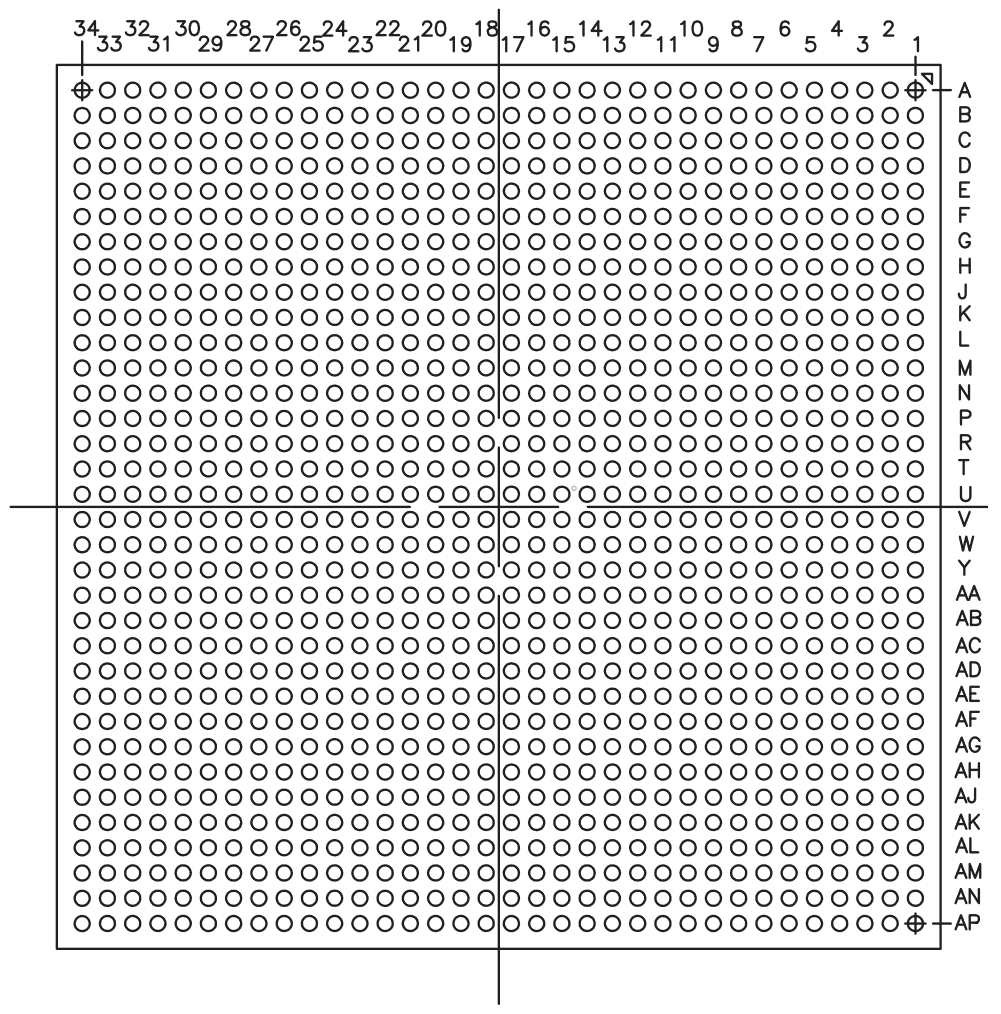

Figure 4-1 ZUM Package, 1158-Pin FCBGA, Bottom View

Figure 4-1 ZUM Package, 1158-Pin FCBGA, Bottom ViewI/O Type Descriptions

| I/O TYPE | DESCRIPTION |

|---|---|

| PWR | Power |

| GND | Ground |

| LVCMOS18_I | LVCMOS 1.8V input |

| LVCMOS18_O | LVCMOS 1.8V output |

| LVCMOS18_B | LVCMOS 1.8V bidirectional |

| LVDS_18_NI | LVDS 1.8V negative input |

| LVDS_18_PI | LVDS 1.8V positive input |

| LVDS_18_NO | LVDS 1.8V negative output |

| LVDS_18_PO | LVDS 1.8V positive output |

| LVDCI_18_I | Low-voltage digitally controlled impedance 1.8V input |

| LVDCI_18_O | Low-voltage digitally controlled impedance 1.8V output |

| MGTHRX_18_NI | GTH Receiver Differential 1.8V negative input |

| MGTHRX_18_PI | GTH Receiver Differential 1.8V positive input |

| MGTHTX_18_NO | GTH Receiver Differential 1.8V negative output |

| MGTHTX_18_PO | GTH Receiver Differential 1.8V positive output |

| MGTREFCLK_NI | GTH Receiver RefClk Differential 1.8V negative input |

| MGTREFCLK_PI | GTH Receiver RefClk Differential 1.8V positive input |

| NC | No connection |

Table 4-1 Pin Functions

| PIN | I/O TYPE(1) | ACTIVE (HI OR LO) | CLOCK SYSTEM | DESCRIPTION | |

|---|---|---|---|---|---|

| NAME | NO. | ||||

| SYS_ARSTZ | G25 | LVCMOS18_I | LO = 0 | — | DLPC964 Reset |

| I2C_ADDR_SEL[0] | M25 | LVCMOS18_I | HI = 1 | — | DLPC964 Slave I2C Address Bit 0 |

| I2C_ADDR_SEL[1] | D26 | LVCMOS18_I | HI | — | DLPC964 Slave I2C Address Bit 1 |

| I2C_SCL | B23 | LVCMOS18_B | — | — | DLPC964 Slave I2C Clock. Requires an external 2.2kΩ pullup resistor |

| I2C_SDA | B25 | LVCMOS18_B | — | I2C_SCL | DLPC964 Slave I2C Data. Requires an external 2.2kΩ pullup resistor |

| SYS_CLK100_N | H24 | LVDS_18_NI | — | Reference clock | 100MHz Differential Reference Clock (N) |

| SYS_CLK100_P | J24 | LVDS_18_PI | — | Reference clock | 100MHz Differential Reference Clock (P) |

| CCLK_0 | V25 | LVCMOS18_O | — | Flash interface clock | Connect to Configuration Flash device CLK. |

| FLASH_MISO | A24 | LVCMOS18_I | — | CCLK_0 | Connect to Configuration Flash MISO. |

| FLASH_MOSI | A23 | LVCMOS18_O | — | CCLK_0 | Connect to Configuration Flash device MOSI. |

| FLASH_CSZ | C24 | LVCMOS18_O | LO | CCLK_0 | Connect to Configuration Flash device CSZ. |

| BLKADDR[0] | B26 | LVCMOS18_I | HI | — | Block Address bit 0 |

| BLKADDR[1] | A26 | LVCMOS18_I | HI | — | Block Address bit 1 |

| BLKADDR[2] | F24 | LVCMOS18_I | HI | — | Block Address bit 2 |

| BLKADDR[3] | F25 | LVCMOS18_I | HI | — | Block Address bit 3 |

| BLKADDR[4] | E24 | LVCMOS18_I | HI | — | Block Address bit 4 |

| BLKMODE[0] | C27 | LVCMOS18_I | HI | — | Block Mode bit 0 |

| BLKMODE[1] | A25 | LVCMOS18_I | HI | — | Block Mode bit 1 |

| BLKLOADZ | B27 | LVDCI_18_O | LO | — | Connect to Apps FPGA BLKLOADZ. |

| LOAD2 | D25 | LVCMOS18_I | HI | — | Enables Load-2 functionality of the DMD. Includes an internal pulldown |

| WDT_ENABLEZ | J22 | LVCMOS18_I | LO | — | DMD Mirror Clocking Pulse Watchdog Timer Enable. Includes an internal pulldown |

| MCP_START | J25 | LVCMOS18_I | HI | — | Initiates a Mirror Clocking Pulse (MCP) |

| MCP0_ACTIVE | E27 | LVDCI_18_O | HI | — | Connect to Apps FPGA MCP_ACTIVE0. |

| MCP1_ACTIVE | D27 | LVDCI_18_O | HI | — | Connect to Apps FPGA MCP_ACTIVE1. |

| MCP2_ACTIVE | E26 | LVDCI_18_O | HI | — | Connect to Apps FPGA MCP_ACTIVE2. |

| MCP3_ACTIVE | H25 | LVDCI_18_O | HI | — | Connect to Apps FPGA MCP_ACTIVE3. |

| DMDLOAD_REQ | M22 | LVCMOS18_I | HI | — | Connect to Apps FPGA DMDLOAD_REQ. |

| DMD_GTREFCLK_IN_A_N | AB30 | LVDS_18_NI | — | Reference clock | DMD Bus A Reference Clock Input. 100Ω internal LVDS termination |

| DMD_GTREFCLK_IN_A_P | AB29 | LVDS_18_PI | — | ||

| DMD_GTREFCLK_IN_B_N | AB5 | LVDS_18_NI | — | Reference clock | DMD Bus B Reference Clock Input. 100Ω internal LVDS termination |

| DMD_GTREFCLK_IN_B_P | AB6 | LVDS_18_PI | — | ||

| DMD_GTREFCLK_IN_C_N | M30 | LVDS_18_NI | — | Reference clock | DMD Bus C Reference Clock Input. 100Ω internal LVDS termination |

| DMD_GTREFCLK_IN_C_P | M29 | LVDS_18_PI | — | ||

| DMD_GTREFCLK_IN_D_N | M5 | LVDS_18_NI | — | Reference clock | DMD Bus D Reference Clock Input. 100Ω internal LVDS termination |

| DMD_GTREFCLK_IN_D_P | M6 | LVDS_18_PI | — | ||

| DMD_DCLK_AN | AK34 | MGTHTX_18_NO | — | — | Output Bus A Clock to DMD |

| DMD_DCLK_AP | AK33 | MGTHTX_18_PO | — | — | |

| DMD_DCLK_BN | AJ3 | MGTHTX_18_NO | — | — | Output Bus B Clock to DMD |

| DMD_DCLK_BP | AJ4 | MGTHTX_18_PO | — | — | |

| DMD_DCLK_CN | G32 | MGTHTX_18_NO | — | — | Output Bus C Clock to DMD |

| DMD_DCLK_CP | G31 | MGTHTX_18_PO | — | — | |

| DMD_DCLK_DN | G3 | MGTHTX_18_NO | — | — | Output Bus D Clock to DMD |

| DMD_DCLK_DP | G4 | MGTHTX_18_PO | — | — | |

| DMD_D_AN[0] | AP34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 0 to DMD |

| DMD_D_AP[0] | AP33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[1] | AN32 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 1 to DMD |

| DMD_D_AP[1] | AN31 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[2] | AM34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 2 to DMD |

| DMD_D_AP[2] | AM33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[3] | AJ32 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 3 to DMD |

| DMD_D_AP[3] | AJ31 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[4] | AH34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 4 to DMD |

| DMD_D_AP[4] | AH33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[5] | AF34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 5 to DMD |

| DMD_D_AP[5] | AF33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[6] | AD34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 6 to DMD |

| DMD_D_AP[6] | AD33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_AN[7] | AB34 | MGTHTX_18_NO | — | DMD_DCLK_A | Output Bus A Data bit 7 to DMD |

| DMD_D_AP[7] | AB33 | MGTHTX_18_PO | — | DMD_DCLK_A | |

| DMD_D_BN[0] | AB1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 0 to DMD |

| DMD_D_BP[0] | AB2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[1] | AD1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 1 to DMD |

| DMD_D_BP[1] | AD2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[2] | AF1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 2 to DMD |

| DMD_D_BP[2] | AF2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[3] | AH1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 3 to DMD |

| DMD_D_BP[3] | AH2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[4] | AK1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 4 to DMD |

| DMD_D_BP[4] | AK2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[5] | AM1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 5 to DMD |

| DMD_D_BP[5] | AM2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[6] | AN3 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 6 to DMD |

| DMD_D_BP[6] | AN4 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_BN[7] | AP1 | MGTHTX_18_NO | — | DMD_DCLK_B | Output Bus B Data bit 7 to DMD |

| DMD_D_BP[7] | AP2 | MGTHTX_18_PO | — | DMD_DCLK_B | |

| DMD_D_CN[0] | A32 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 0 to DMD |

| DMD_D_CP[0] | A31 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[1] | B34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 1 to DMD |

| DMD_D_CP[1] | B33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[2] | D34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 2 to DMD |

| DMD_D_CP[2] | D33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[3] | F34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 3 to DMD |

| DMD_D_CP[3] | F33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[4] | H34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 4 to DMD |

| DMD_D_CP[4] | H33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[5] | K34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 5 to DMD |

| DMD_D_CP[5] | K33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[6] | M34 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 6 to DMD |

| DMD_D_CP[6] | M33 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_CN[7] | N32 | MGTHTX_18_NO | — | DMD_DCLK_C | Output Bus C Data bit 7 to DMD |

| DMD_D_CP[7] | N31 | MGTHTX_18_PO | — | DMD_DCLK_C | |

| DMD_D_DN[0] | N3 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 0 to DMD |

| DMD_D_DP[0] | N4 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[1] | M1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 1 to DMD |

| DMD_D_DP[1] | M2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[2] | K1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 2 to DMD |

| DMD_D_DP[2] | K2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[3] | H1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 3 to DMD |

| DMD_D_DP[3] | H2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[4] | F1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 4 to DMD |

| DMD_D_DP[4] | F2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[5] | D1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 5 to DMD |

| DMD_D_DP[5] | D2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[6] | B1 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 6 to DMD |

| DMD_D_DP[6] | B2 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| DMD_D_DN[7] | A3 | MGTHTX_18_NO | — | DMD_DCLK_D | Output Bus D Data bit 7 to DMD |

| DMD_D_DP[7] | A4 | MGTHTX_18_PO | — | DMD_DCLK_D | |

| GTRX_CH0_REFCLK_N | R28 | MGTREFCLK_NI | — | Reference clock | Input CH0 Reference Clock. 100Ω internal LVDS termination |

| GTRX_CH0_REFCLK_P | R27 | MGTREFCLK_PI | — | ||

| GTRX_CH1_REFCLK_N | W28 | MGTREFCLK_NI | — | Reference clock | Input CH1 Reference Clock. 100Ω internal LVDS termination |

| GTRX_CH1_REFCLK_P | W27 | MGTREFCLK_PI | — | ||

| GTRX_CH2_REFCLK_N | R7 | MGTREFCLK_NI | — | Reference clock | Input CH2 Reference Clock. 100Ω internal LVDS termination |

| GTRX_CH2_REFCLK_P | R8 | MGTREFCLK_PI | — | ||

| GTRX_CH3_REFCLK_N | W7 | MGTREFCLK_NI | — | Reference clock | Input CH3 Reference Clock. 100Ω internal LVDS termination |

| GTRX_CH3_REFCLK_P | W8 | MGTREFCLK_PI | — | ||

| CH0_GTRX_N[0] | T30 | MGTHRX_18_NI | — | GTRX_CH0_REFCLK | Input Bus CH0 Data bit 0. 100Ω internal LVDS termination |

| CH0_GTRX_P[0] | T29 | MGTHRX_18_PI | — | ||

| CH0_GTRX_N[1] | R32 | MGTHRX_18_NI | — | GTRX_CH0_REFCLK | Input Bus CH0 Data bit 1. 100Ω internal LVDS termination |

| CH0_GTRX_P[1] | R31 | MGTHRX_18_PI | — | ||

| CH0_GTRX_N[2] | P30 | MGTHRX_18_NI | — | GTRX_CH0_REFCLK | Input Bus CH0 Data bit 2. 100Ω internal LVDS termination |

| CH0_GTRX_P[2] | P29 | MGTHRX_18_PI | — | ||

| CH1_GTRX_N[0] | AA32 | MGTHRX_18_NI | — | GTRX_CH1_REFCLK | Input Bus CH1 Data bit 0. 100Ω internal LVDS termination |

| CH1_GTRX_P[0] | AA31 | MGTHRX_18_PI | — | ||

| CH1_GTRX_N[1] | Y30 | MGTHRX_18_NI | — | GTRX_CH1_REFCLK | Input Bus CH1 Data bit 1. 100Ω internal LVDS termination |

| CH1_GTRX_P[1] | Y29 | MGTHRX_18_PI | — | ||

| CH1_GTRX_N[2] | V30 | MGTHRX_18_NI | — | GTRX_CH1_REFCLK | Input Bus CH1 Data bit 2. 100Ω internal LVDS termination |

| CH1_GTRX_P[2] | V29 | MGTHRX_18_PI | — | ||

| CH2_GTRX_N[0] | T5 | MGTHRX_18_NI | — | GTRX_CH2_REFCLK | Input Bus CH2 Data bit 0. 100Ω internal LVDS termination |

| CH2_GTRX_P[0] | T6 | MGTHRX_18_PI | — | ||

| CH2_GTRX_N[1] | R3 | MGTHRX_18_NI | — | GTRX_CH2_REFCLK | Input Bus CH2 Data bit 1. 100Ω internal LVDS termination |

| CH2_GTRX_P[1] | R4 | MGTHRX_18_PI | — | ||

| CH2_GTRX_N[2] | P5 | MGTHRX_18_NI | — | GTRX_CH2_REFCLK | Input Bus CH2 Data bit 2. 100Ω internal LVDS termination |

| CH2_GTRX_P[2] | P6 | MGTHRX_18_PI | — | ||

| CH3_GTRX_N[0] | AA3 | MGTHRX_18_NI | — | GTRX_CH3_REFCLK | Input Bus CH3 Data bit 0. 100Ω internal LVDS termination |

| CH3_GTRX_P[0] | AA4 | MGTHRX_18_PI | — | ||

| CH3_GTRX_N[1] | Y5 | MGTHRX_18_NI | — | GTRX_CH3_REFCLK | Input Bus CH3 Data bit 1. 100Ω internal LVDS termination |

| CH3_GTRX_P[1] | Y6 | MGTHRX_18_PI | — | ||

| CH3_GTRX_N[2] | V5 | MGTHRX_18_NI | — | GTRX_CH3_REFCLK | Input Bus CH3 Data bit 2. 100Ω internal LVDS termination |

| CH3_GTRX_P[2] | V6 | MGTHRX_18_PI | — | ||

| HSSI_BUS_ERR | AJ12 | LVDCI_18_O | HI | — | Connect to Apps FPGA HSSI_BUS_ERR. |

| HSSI_ERR_LATCH_RST | AN12 | LVDCI_18_O | LO | — | Connect to Latch Clear on DMD board. |

| EXT_HSSI_RST | AJ14 | LVCMOS18_I | HI | — | Connect to Apps FPGA EXT_HSSI_RST. |

| HSSI_RST_ACT | AK12 | LVDCI_18_O | HI | — | Connect to Apps FPGA HSSI_RST_ACT. |

| DMD_LS_CLK_N | AP11 | LVDS_18_NO | — | — | Output LS Bus Clock to DMD |

| DMD_LS_CLK_P | AP12 | LVDS_18_PO | — | — | |

| DMD_LS_WDATA_N | AP14 | LVDS_18_NO | — | DMD_LS_CLK | Output WData Bus to DMD |

| DMD_LS_WDATA_P | AN14 | LVDS_18_PO | — | DMD_LS_CLK | |

| DMD_LS_RDATA_A | AM8 | LVCMOS18_I | — | DMD_LS_CLK | Input Bus RData bit A |

| DMD_LS_RDATA_B | AN8 | LVCMOS18_I | — | DMD_LS_CLK | Input Bus RData bit B |

| DMD_LS_RDATA_C | AN9 | LVCMOS18_I | — | DMD_LS_CLK | Input Bus RData bit C |

| DMD_LS_RDATA_D | AP9 | LVCMOS18_I | — | DMD_LS_CLK | Input Bus RData bit D |

| DMD_DMUX | AM12 | LVCMOS18_I | HI | — | Connect to DMUX_LATCHED on DMD board. |

| IRQZ | E23 | LVDCI_18_O | LO | — | Connect to Apps FPGA IRQZ. |

| DMD_RESERVED | AM13 | LVCMOS18_B | — | — | Connect to RESERVED pin on DMD. |

| PARKZ | AK9 | LVCMOS18_I | LO | — | Immediately parks the DMD when asserted Low |

| RXLPMEN | D24 | LVCMOS18_I | HI | — | Enables Aurora 64B/66B Receiver Low Power Mode |

| DMD_PWREN | AL9 | LVDCI_18_O | HI | — | Connect to DMD Power Enable on DMD board. |

| DMDPWRGOOD | P24 | LVCMOS18_I | HI | — | Connect to DMDPWRGOOD on DMD board. |

| PWRGOOD | H22 | LVCMOS18_I | HI | — | Connect to Power Good on DLPC964 Controller board. |

| LED_PWR | AL14 | LVDCI_18_O | HI | — | Enable control output for LED Power Supply |

| STATUS_LED_R1 | AM10 | LVDCI_18_O | HI | — | Controller PLL clock circuitry NOT locked Indicator LED output |

| STATUS_LED_R2 | AK13 | LVDCI_18_O | HI | — | DMD HSSI interface Sync errors detected Indicator LED output |

| STATUS_LED_G1 | AL10 | LVDCI_18_O | HI | — | Controller PLL clock circuitry locked Indicator LED output |

| STATUS_LED_G2 | AK8 | LVDCI_18_O | HI | — | No DMD HSSI interface Sync errors detected Indicator LED output |

| LED_HEARTBEAT | AK14 | LVDCI_18_O | HI | — | Heartbeat Indicator LED output |

| INIT_DONE | F23 | LVDCI_18_O | HI | — | Connect to Apps FPGA C964_INIT_DONE |

| M0_0 | AA10 | LVCMOS18_I | — | — | DLPC964 Configuration — connect to 1.8V |

| M1_0 | Y10 | LVCMOS18_I | — | — | DLPC964 Configuration — connect to GND |

| M2_0 | W10 | LVCMOS18_I | — | — | DLPC964 Configuration — connect to GND |

| TDO_0 | AA25 | LVCMOS18_O | — | — | JTAG Data out of DLPC964. Connects to JTAG return TDO on JTAG connector |

| TDI_0 | AB25 | LVCMOS18_I | — | — | JTAG Data into DLPC964. Connects to JTAG input TDI on JTAG connector |

| TMS_0 | W25 | LVCMOS18_I | — | — | JTAG Data. Connects to JTAG TMS on JTAG connector |

| TCK_0 | Y25 | LVCMOS18_I | — | — | JTAG Clock. Connects to JTAG TCK on JTAG connector |

| INIT_B_0 | T10 | LVCMOS18_O | — | — | DLPC964 Configuration. Pull up to 1.8V with a 4.7KΩ resistor. |

| CFGBVS_0 | U10 | LVCMOS18_I | — | — | DLPC964 Configuration. Connect to GND. |

| PROGRAM_B_0 | V10 | LVCMOS18_O | — | — | DLPC964 Configuration. Pull up to 1.8V with a 4.7KΩ resistor. |

| DONE_0 | AB10 | LVCMOS18_O | HI | — | DLPC964 Configuration. Pull up to 1.8V with a 330Ω resistor. |

| K_DATA[0] | K22 | LVDCI_18_O | — | CLK_K | Bit 64 of user_k_tdata[] |

| K_DATA[1] | K23 | LVDCI_18_O | — | CLK_K | Bit 65 of user_k_tdata[] |

| K_DATA[2] | M23 | LVDCI_18_O | — | CLK_K | Bit 66 of user_k_tdata[] |

| K_VALID | K24 | LVDCI_18_O | — | CLK_K | |

|

K_DATA[3] |

L23 | LVDCI_18_O | — | CLK_K | Bit 67 of user_k_tdata[] |

| CLK_K | L24 | LVDCI_18_I | — | — | K_DATA Clock input (156.25MHz) |

|

K_DATA[4] |

L25 | LVDCI_18_O | — |

CLK_K |

Bit 68 of user_k_tdata[] |

| FAN_PWM | N22 | LVDCI_18_O | — | — | To DLPC964 Controller Fan connector |

| TESTMUX0 | AE11 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX1 | AE13 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX2 | AE14 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX3 | AF10 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX4 | AF11 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX5 | AF13 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX6 | AF14 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX7 | AG10 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX8 | AG11 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX9 | AG12 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX10 | AG13 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX11 | AH12 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX12 | AH13 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX13 | AH14 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX14 | AJ9 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| TESTMUX15 | AJ10 | LVDCI_18_O | — | — | No connect. For access to test point output route to test via. |

| VN_0 | Y17 | — | — | — | Connect to GND. |

| VP_0 | W18 | — | — | — | Connect to GND. |

| VREFN_0 | W17 | — | — | — | Connect to GND. |

| VREFP_0 | Y18 | — | — | — | Connect to GND. |

| DXN_0 | AA17 | — | — | — | Connect to GND. |

| DXP_0 | AA18 | — | — | — | Connect to GND. |

| VCCADC_0 | V18 | PWR | — | — | Connect to 1.8V. |

| VCCBATT_0 | U25 | PWR | — | — | Connect to GND. |

| VCCO | A12, A22, AC11, AE10, AE20, AF17, AG14, AG24, AH11, AH21, AJ8, AJ18, AK15, AK25, AL12, AL22, AM9, AM19, AN16, AN26, AP13, AP23, B9, B19, C16, C26, D13, D23, E10, E20, F17, G14, G24, H11, H21, J18, K15, K25, L12, L22, M19, N16, P13, P23 | PWR | — | — | Power. P1V8 |

| VCCINT | AA12, AA16, AA22, AA24, AB11, AB15, AB17, AB23, AC10, AC12, AC16, AC18, AC22, AC24, AD11, AD15, AD17, AD23, AD25, R10, R12, R14, R16, R18, R22, R24, T11, T13, T15, T17, T21, T23, T25, U12, U14, U16, U18, U22, U24, V11, V15, V23, W12, W16, W22, W24, Y11, Y15, Y23 | PWR | — | — | Power. P1V0_CORE |

| VCCAUX | AA14, AA20, AB13, AB21, AC14, AC20, AD13, AD21, U20, V13, V21, W14, W20, Y13, Y21 | PWR | — | — | Aux Power. P1V8 |

| VCCBRAM | AB19, AD19, R20, T19, V19, Y19 | PWR | — | — | Power. P1V0_CORE |

| MGTAVCC | AA29, AC6, AC29, AE6, AE29, AG6, AG29, AJ6, AJ29, AL6, AL29, AN6, AN29, C6, C29, E6, E29, G6, G29, J6, J29, L6, L29, N6, N29, R6, R29 | PWR | — | — | Power. P1V0_MGT |

| MGTVCCAUX | U6, U29, W6, W29 | PWR | — | — | Aux Power. P1V8 |

| MGTAVTT | AC2, AC33, AD3, AD32, AG2, AG33, AH3, AH32, AL2, AL33, AM3, AM32, C2, C33, D3, D32, G2, G33, H3, H32, L2, L33, M3, M32, R2, R33, T3, T32, W2, W33, Y3, Y32 | PWR | — | — | Power. P1V2 |

| GNDADC_0 | V17 | GND | — | — | ADC Ground |

| GND | A1, A2, A5, A6, A7, A17, A27, A28, A29, A30, A33, A34, AA1, AA2, AA9, AA11, AA13, AA15, AA19, AA21, AA23, AA26, AA30, AA33, AA34, AB3, AB4, AB7, AB8, AB9, AB12, AB14, AB16, AB18, AB20, AB22, AB24, AB26, AB27, AB28, AB31, AB32, AC1, AC5, AC9, AC13, AC15, AC17, AC19, AC21, AC23, AC25, AC26, AC30, AC34, AD4, AD7, AD8, AD9, AD10, AD12, AD20, AD22, AD24, AD26, AD27, AD28, AD31, AE1, AE2, AE5, AE9, AE15, AE25, AE26, AE30, AE33, AE34, AF3, AF4, AF7, AF8, AF9, AF12, AF22, AF26, AF27, AF28,AF31, AF32, AG1, AG5, AG7, AG8, AG9, AG19, AG26, AG27, AG28, AG30, AG34, AH4, AH7, AH8, AH9, AH16, AH26, AH27, AH28, AH31, AJ1, AJ2, AJ5, AJ7, AJ13, AJ23, AJ28, AJ30, AJ33, AJ34, AK3, AK4, AK7, AK10, AK20, AK28, AK31, AK32, AL1, AL5, AL7, AL17, AL27, AL28, AL30, AL34, AM4, AM7, AM14, AM24, AM28, AM31, AN1, AN2, AN5, AN7, AN11, AN21, AN28, AN30, AN33, AN34, AP3, AP4, AP7, AP8, AP18, AP28, AP31, AP32, B3, B4, B7, B14, B24, B28, B31, B32, C1, C5, C7, C11, C21, C28, C30, C34, D4, D7, D8, D18, D28, D31, E1, E2, E5, E7, E15, E25, E28, E30, E33, E34, F3, F4, F7, F8, F9, F12, F22, F26, F27, F28, F31, F32, G1, G5, G9, G19, G26, G30, G34, H4, H7, H8, H9, H16, H26, H27, H28, H31, J1, J2, J5, J9, J13, J23, J26, J30, J33, J34, K3, K4, K7, K8, K9, K10, K20, K26, K27, K28, K31, K32, L1, L5, L9, L17, L26, L30, L34, M4, M7, M8, M9, M14, M24, M26, M27, M28, M31, N1, N2, N5, N9, N11, N21, N26, N30, N33, N34, P3, P4, P7, P8, P9, P18, P26, P27, P28, P31, P32, R1, R5, R9, R15, R17, R19, R21, R26, R30, R34, T4, T7, T8, T9, T12, T14, T16, T18, T20, T22, T24, T26, T27, T28, T31, U1, U2, U5, U9, U11, U13, U15, U17, U19, U21, U23, U26, U30, U33, U34, V3, V4, V7, V8, V9, V12, V14, V16, V20, V22, V24, V26, V27, V28, V31, V32, W1, W5, W9, W11, W13, W15, W19, W21, W23, W26, W30, W33, Y4, Y7, Y8, Y9, Y12, Y14, Y16, Y20, Y22, Y24, Y26, Y27, Y28, Y31 | GND | — | — | — |

| RESERVED | R23 | — | — | — | Pull up to 1.8V with 100Ω resistor |

| RESERVED | R25 | — | — | — | Pull down to GND with 100Ω resistor |

| RESERVED | AE12 | — | — | — | Pull up to 1.8V with 100Ω resistor |

| RESERVED | AD14 | — | — | — | Pull down to GND with 100Ω resistor |

| RESERVED | G7 | — | — | — | Pull up to 1.2V with 100Ω resistor |

| RESERVED | G8 | — | — | — | Connect to 1.2V |

| RESERVED | G27 | — | — | — | Connect to 1.2V |

| RESERVED | G28 | — | — | — | Pull up to 1.2V with 100Ω resistor |

| UNUSED | A8, A9, A10, A11, A13, A14, A15, A16, A18, A19, A20, A21, A23, A24, AC3, AC4, AC7, AC8, AC27, AC28, AC31, AC32, AD5, AD6, AD16, AD18, AD29, AD30, AE3, AE4, AE7, AE8, AE16, AE17, AE18, AE19, AE21, AE22, AE23, AE24, AE27, AE28, AE31, AE32, AF5, AF6, AF15, AF16, AF18, AF19, AF20, AF21, AF23, AF24, AF25, AF29, AF30, AG3, AG4, AG15, AG16, AG17, AG18, AG20, AG21, AG22, AG23, AG25, AG31, AG32, AH5, AH6, AH10, AH15, AH17, AH18, AH19, AH20, AH22, AH23, AH24, AH25, AH29, AH30, AJ11, AJ15, AJ16, AJ17, AJ19, AJ20, AJ21, AJ22, AJ24, AJ25, AJ26, AJ27, AK5, AK6, AK11, AK16, AK17, AK18, AK19, AK21, AK22, AK23, AK24, AK26, AK27, AK29, AK30, AL3, AL4, AL8, AL11, AL13, AL15, AL16, AL18, AL19, AL20, AL21, AL23, AL24, AL25, AL26, AL31, AL32, AM5, AM6, AM11, AM15, AM16, AM17, AM18, AM20, AM21, AM22, AM23, AM25, AM26, AM27, AM29, AM30, AN13, AN15, AN17, AN18, AN19, AN20, AN22, AN23, AN24, AN25, AN27, AP5, AP6, AP10, AP15, AP16, AP17, AP19, AP20, AP21, AP22, AP24, AP25, AP26, AP27, AP29, AP30, B5, B6, B8, B10, B11, B12, B13, B15, B16, B17, B18, B20, B21, B22, B29, B30, C3, C4, C8, C9, C10, C12, C13, C14, C15, C17, C18, C19, C20, C22, C23, C24, C25, C31, C32, D5, D6, D9, D10, D11, D12, D14, D15, D16, D17, D19, D20, D21, D22, D29, D30, E3, E4, E8, E9, E11, E12, E13, E14, E16, E17, E18, E19, E21, E22, E31, E32, F5, F6, F10, F11, F13, F14, F15, F16, F18, F19, F20, F21, F29, F30, G10, G11, G12, G13, G15, G16, G17, G18, G20, G21, G22, G23, H5, H6, H10, H12, H13, H14, H15, H17, H18, H19, H20, H23, H29, H30, J3, J4, J7, J8, J10, J11, J12, J14, J15, J16, J17, J19, J20, J21, J27, J28, J31, J32, K5, K6, K11, K12, K13, K14, K16, K17, K18, K19, K21, K29, K30, L3, L4, L7, L8, L10, L11, L13, L14, L15, L16, L18, L19, L20, L21, L27, L28, L31, L32, M10, M11, M12, M13, M15, M16, M17, M18, M20, M21, N7, N8, N10, N12, N13, N14, N15, N17, N18, N19, N20, N23, N24, N25, N27, N28, P1, P2, P10, P11, P12, P14, P15, P16, P17, P19, P20, P21, P22, P25, P33, P34, R11, R13, T1, T2, T33, T34, U3, U4, U7, U8, U27, U28, U31, U32, V1, V2, V33, V34, W3, W4, W31, W32, Y1, Y2, Y33, Y34 | NC | |||

(1) I = Input, O = Output, B = Input or Output, GND = Ground, PWR = Power, NC = No Connect.