SBOS637D October 2016 – June 2019 OPA2325 , OPA325 , OPA4325

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- DGK|8

Orderable Information

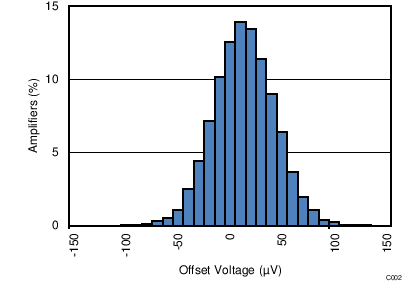

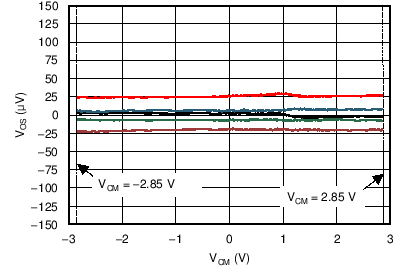

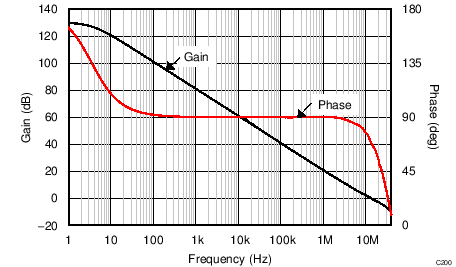

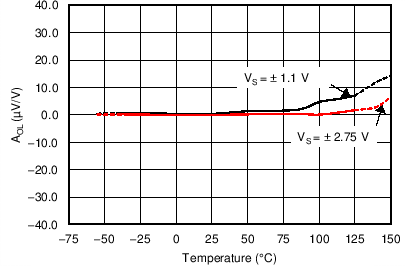

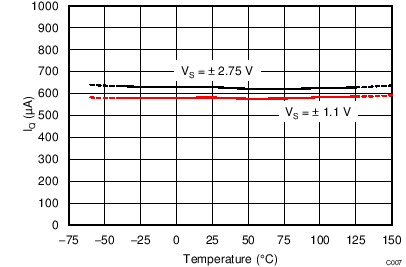

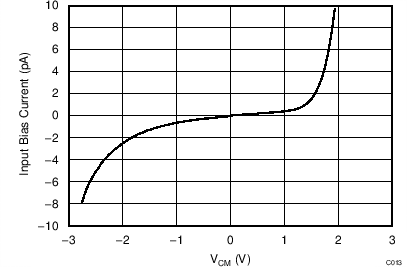

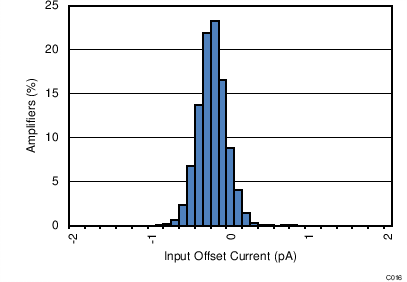

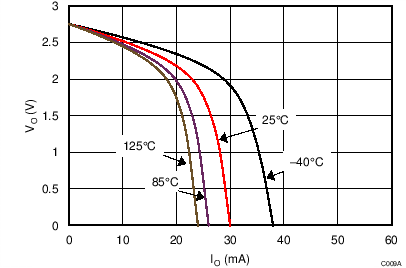

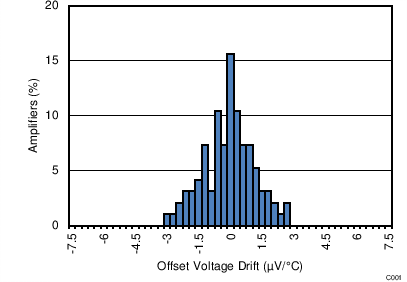

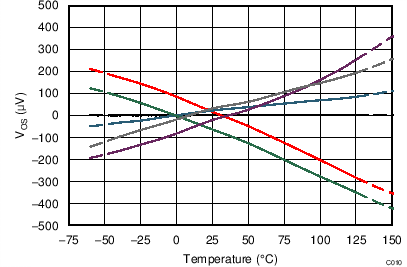

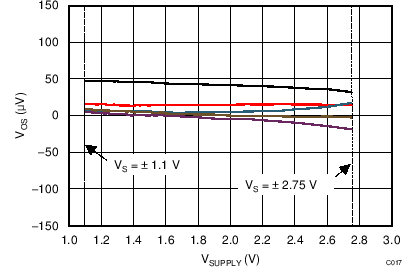

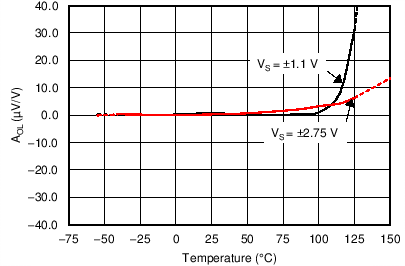

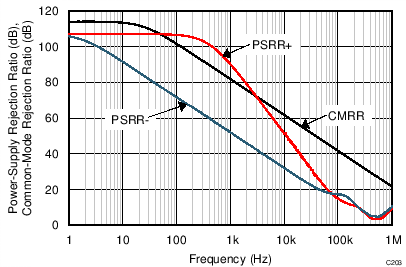

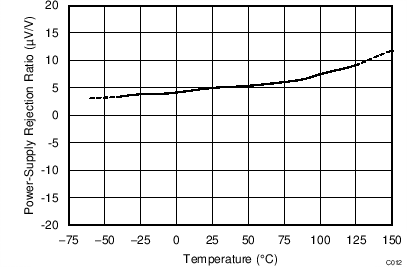

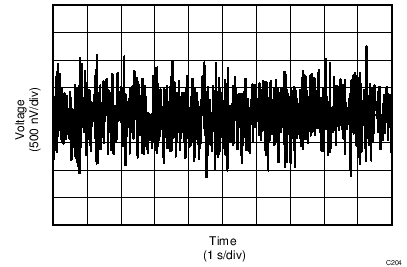

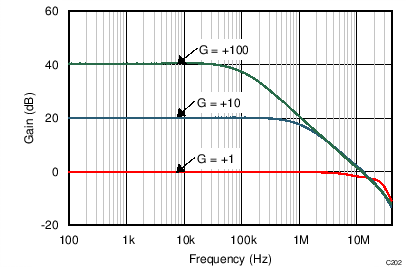

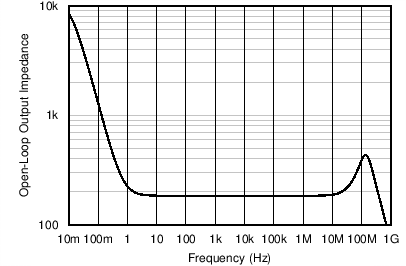

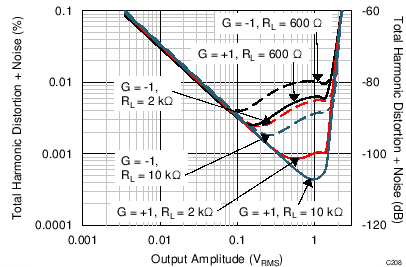

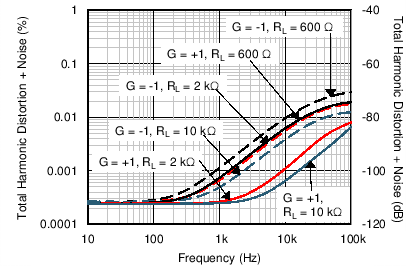

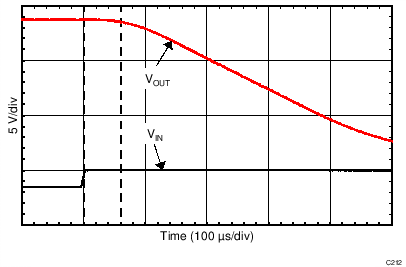

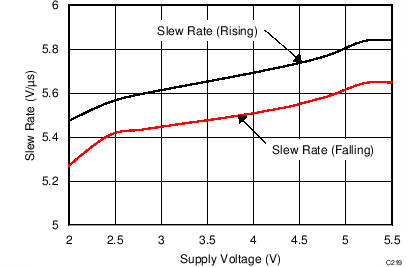

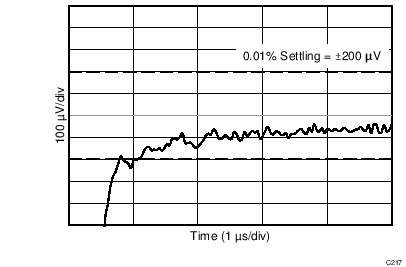

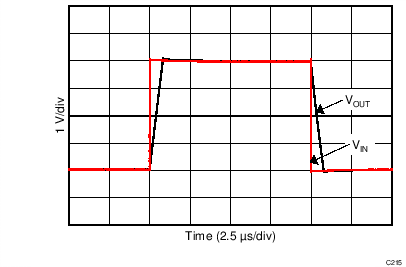

6.8 Typical Characteristics

at TA = 25°C, VCM = VOUT = midsupply, and RL = 10 kΩ (unless otherwise noted)

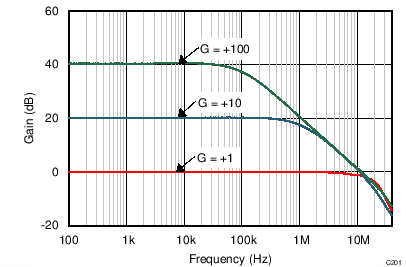

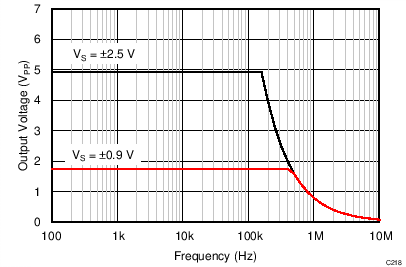

| CL = 15 pF |

| RL = 10 kΩ |

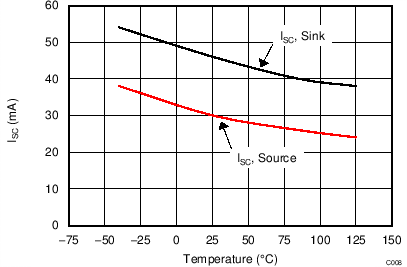

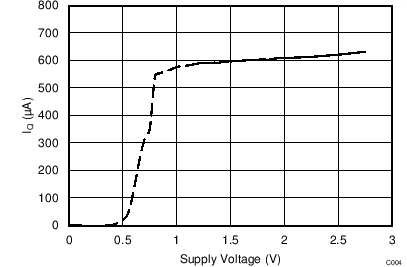

Output Current

| VS = 1.8 V, RL = 10 kΩ, CL = 15 pF |

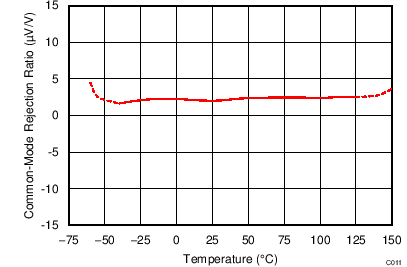

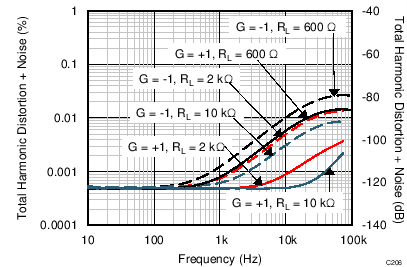

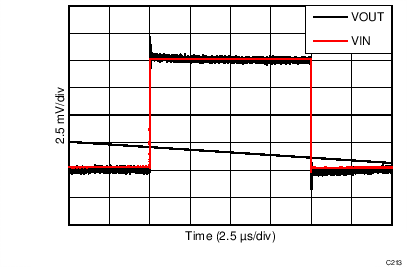

| VIN = 2 VPP, VS = ±2.5 V, filter bandwidth = 500 kHz |

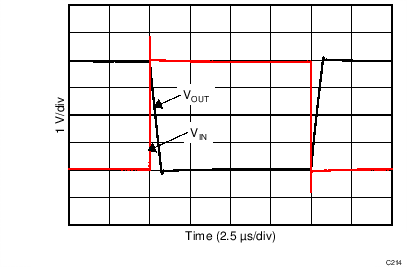

| VIN = 10 mVPP, G = +1, CL = 15 pF |

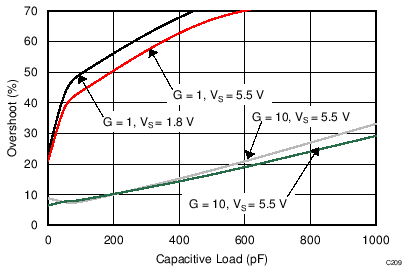

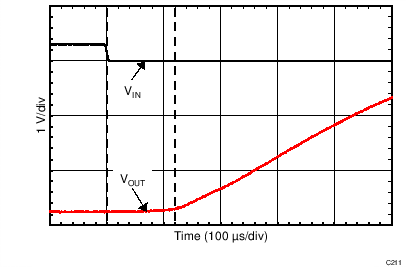

| VIN = 2-V step |

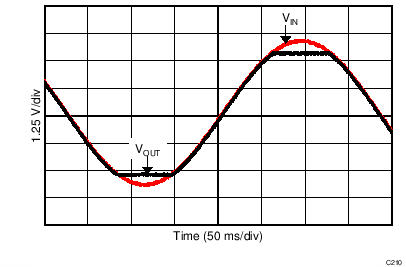

| VIN = 4 VPP, G = –1, CL = 15 pF |

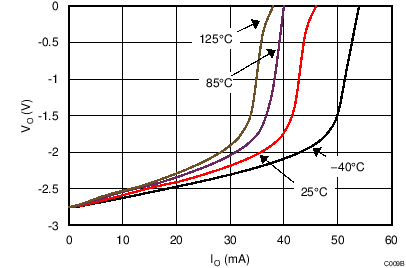

| RL = 2 kΩ |

Output Current

| VS = 5.5 V, RL = 10 kΩ, CL = 15 pF |

| f = 10 kHz, VS = ±2.5 V, filter bandwidth = 500 kHz |

| VIN = 4 VPP, VS = ±2.5 V, filter bandwidth = 500 kHz |

| CL = 15 pF |

| VIN = 2-V step |

| VIN = 4 VPP, G = +1, CL = 15 pF |