JAJSF86F April 2010 – April 2018 DLPC200

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Handling Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 I/O Electrical Characteristics

- 6.6 Video Input Pixel Interface Timing Requirements

- 6.7 I2C Interface Timing Requirements

- 6.8 USB Read Interface Timing Requirements

- 6.9 USB Write Interface Timing Requirements

- 6.10 SPI Slave Interface Timing Requirements

- 6.11 Parallel Flash Interface Timing Requirements

- 6.12 Serial Flash Interface Timing Requirements

- 6.13 Static RAM Interface Timing Requirements

- 6.14 DMD Interface Timing Requirements

- 6.15 DLPA200 Interface Timing Requirements

- 6.16 DDR2 SDR Memory Interface Timing Requirements

- 6.17 Video Input Pixel Interface – Image Sync and Blanking Requirements

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1

DLPC200 System Interfaces

- 8.2.2.1.1 DLPC200 Master, I2C Interface for EDID Programming

- 8.2.2.1.2 USB Interface

- 8.2.2.1.3 Bus Protocol

- 8.2.2.1.4 SPI Slave Interface

- 8.2.2.1.5 Parallel Flash Memory Interface

- 8.2.2.1.6 Serial Flash Memory Interface

- 8.2.2.1.7 SRAM Interface

- 8.2.2.1.8 DDR2 SDR Memory Interface

- 8.2.2.1.9 Projector Image and Control Port Signals

- 8.2.2.1.10 SDRAM Memory

- 8.2.2.1

DLPC200 System Interfaces

- 8.2.3 Application Curve

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

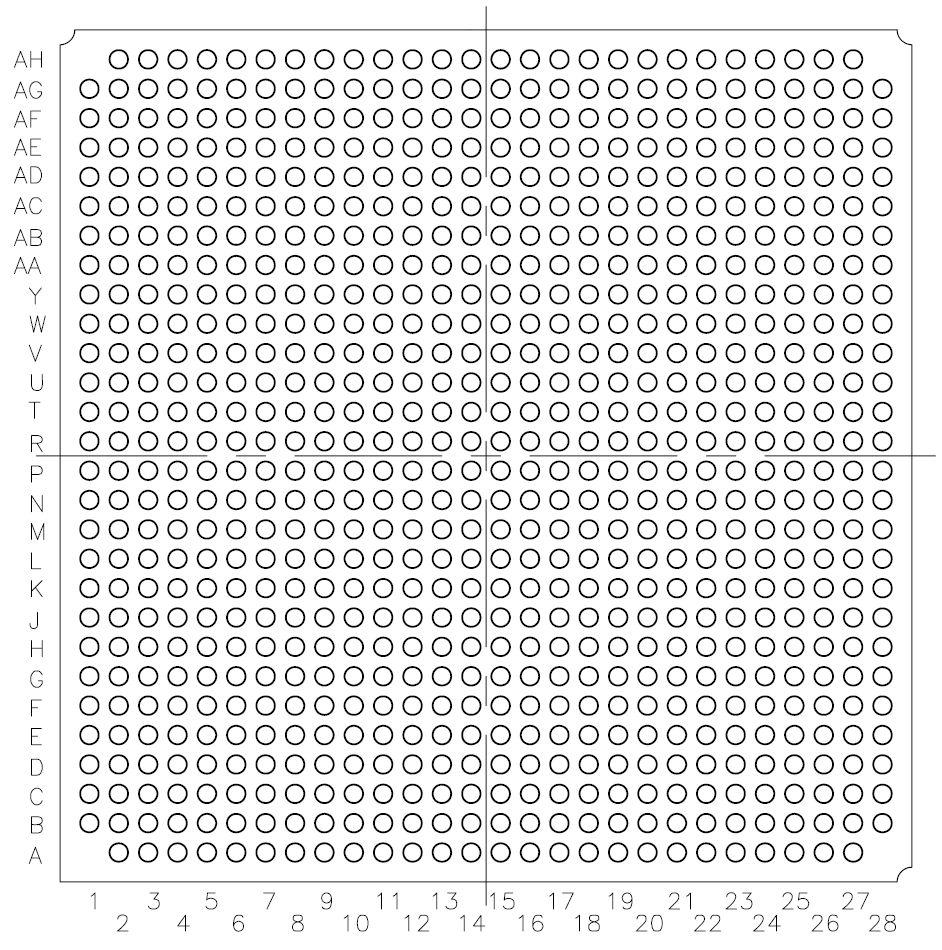

5 Pin Configuration and Functions

BGA

780 PINS

Pin Functions

| PIN | I/O

TYPE(1) |

CLOCK SYSTEM | DESCRIPTION | |||

|---|---|---|---|---|---|---|

| NAME | NUMBER | |||||

| PORT 1 VIDEO DATA AND CONTROL(2) | ||||||

| PORT1_CLK | J2 | I3 | Pixel clock (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_VSYNC | N3 | PORT1_CLK | Vertical sync; weak pullup applied | |||

| PORT1_HSYNC | P1 | PORT1_CLK | Horizontal sync; weak pullup applied | |||

| PORT1_IVALID | P2 | PORT1_CLK | Data valid (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D0 | D2 | PORT1_CLK | Pixel data – Blue 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D1 | D3 | PORT1_CLK | Pixel data – Blue 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D2 | F5 | PORT1_CLK | Pixel data – Blue 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D3 | D1 | PORT1_CLK | Pixel data – Blue 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D4 | F3 | PORT1_CLK | Pixel data – Blue 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D5 | G4 | PORT1_CLK | Pixel data – Blue 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D6 | F1 | PORT1_CLK | Pixel data – Blue 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D7 | G3 | PORT1_CLK | Pixel data – Blue 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D8 | H5 | PORT1_CLK | Pixel data – Green 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D9 | H4 | PORT1_CLK | Pixel data – Green 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D10 | G2 | PORT1_CLK | Pixel data – Green 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D11 | J4 | PORT1_CLK | Pixel data – Green 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D12 | H3 | PORT1_CLK | Pixel data – Green 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D13 | J3 | PORT1_CLK | Pixel data – Green 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D14 | K3 | PORT1_CLK | Pixel data – Green 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D15 | L1 | PORT1_CLK | Pixel data – Green 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D16 | L3 | PORT1_CLK | Pixel data – Red 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D17 | L4 | PORT1_CLK | Pixel data – Red 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D18 | M4 | PORT1_CLK | Pixel data – Red 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D19 | K1 | PORT1_CLK | Pixel data – Red 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D20 | M1 | PORT1_CLK | Pixel data – Red 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D21 | K2 | PORT1_CLK | Pixel data – Red 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D22 | M2 | PORT1_CLK | Pixel data – Red 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_D23 | M3 | PORT1_CLK | Pixel data – Red 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_HPD | E15 | B2 | HDMI hotplug detect, (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT1_SYNCDET | J22 | HDMI input sync detect, (if not used, apply 10-kΩ pulldown to DGND) | ||||

| PORT 2 VIDEO DATA AND CONTROL(2) | ||||||

| PORT2_CLK | Y2 | I1 | Pixel clock (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_VSYNC | AF2 | PORT2_CLK | Vertical sync; weak pullup applied | |||

| PORT2_HSYNC | AB6 | PORT2_CLK | Horizontal sync; weak pullup applied | |||

| PORT2_IVALID | W1 | PORT2_CLK | Data valid (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D0 | Y1 | PORT2_CLK | Pixel data – Blue 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D1 | AE1 | PORT2_CLK | Pixel data – Blue 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D2 | U2 | PORT2_CLK | Pixel data – Blue 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D3 | AD12 | PORT2_CLK | Pixel data – Blue 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D4 | AB1 | PORT2_CLK | Pixel data – Blue 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D5 | V3 | PORT2_CLK | Pixel data – Blue 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D6 | U5 | PORT2_CLK | Pixel data – Blue 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D7 | T3 | PORT2_CLK | Pixel data – Blue 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D8 | AD1 | PORT2_CLK | Pixel data – Green 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D9 | AA3 | PORT2_CLK | Pixel data – Green 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D10 | R6 | PORT2_CLK | Pixel data – Green 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D11 | W3 | PORT2_CLK | Pixel data – Green 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D12 | AB5 | PORT2_CLK | Pixel data – Green 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D13 | AD3 | PORT2_CLK | Pixel data – Green 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D14 | AD5 | PORT2_CLK | Pixel data – Green 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D15 | AD4 | PORT2_CLK | Pixel data – Green 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D16 | AE5 | PORT2_CLK | Pixel data – Red 0 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D17 | AC11 | PORT2_CLK | Pixel data – Red 1 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D18 | AB8 | PORT2_CLK | Pixel data – Red 2 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D19 | AC7 | PORT2_CLK | Pixel data – Red 3 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D20 | AG4 | PORT2_CLK | Pixel data – Red 4 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D21 | AE4 | PORT2_CLK | Pixel data – Red 5 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D22 | AF5 | PORT2_CLK | Pixel data – Red 6 (if not used, apply 10-kΩ pulldown to DGND) | |||

| PORT2_D23 | AF3 | PORT2_CLK | Pixel data – Red 7 (if not used, apply 10-kΩ pulldown to DGND) | |||

| SYNC IN/SYNC OUT | ||||||

| PORT1_Trig_in | F2 | I3 | PORT1_CLK | Alternate sync for port 1; treated as Vsync; weak pullup applied | ||

| PORT1_Sync_out | H6 | O3 | Async | Reserved for future use | ||

| PORT2_Trig_in | AB7 | I1 | PORT2_CLK | Alternate sync for port 2; treated as vsync; weak pullup applied | ||

| PORT2_Sync_out | Y3 | O1 | Async | Reserved for future use | ||

| CONTROL INTERFACES (I2C, USB, SPI) | ||||||

| USB_CLK | B15 | I3 | USB clock input (48 MHz), feeds a PLL (if not used, apply 10-kΩ pulldown to DGND) | |||

| USB_CTRL0 | B17 | I3 | USB_CLK | USB I/F FIFO programmable level (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_CTRL1 | A26 | I3 | USB_CLK | USB I/F FIFO-full flag (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_CTRL2 | D22 | I3 | USB_CLK | USB I/F FIFO-empty flag (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_CTRL3 | C19 | I3 | USB_CLK | Reserved for future use (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_CTRL4 | D16 | I3 | USB_CLK | Reserved for future use (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_CTRL5 | G17 | I3 | USB_CLK | Reserved for future use (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_FD0 | G16 | B2 | USB_CLK | USB interface data bus (if not used, apply 10-kΩ pulldown to DGND) | ||

| USB_FD1 | C26 | |||||

| USB_FD2 | F17 | |||||

| USB_FD3 | C22 | |||||

| USB_FD4 | E18 | |||||

| USB_FD5 | B18 | |||||

| USB_FD6 | F18 | |||||

| USB_FD7 | E19 | |||||

| USB_FD8 | B23 | |||||

| USB_FD9 | D25 | |||||

| USB_FD10 | C21 | |||||

| USB_FD11 | D24 | |||||

| USB_FD12 | B19 | |||||

| USB_FD13 | E25 | |||||

| USB_FD14 | G18 | |||||

| USB_FD15 | C15 | |||||

| USB_PA02 | D23 | O3 | USB_CLK | USB I/F FIFO output enable for reads (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_PA04 | G15 | O3 | USB_CLK | USB I/F FIFO address(0) (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_PA05 | A22 | O3 | USB_CLK | USB I/F FIFO address(1) (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_PA06 | A25 | O3 | USB_CLK | USB I/F FIFO packet end trigger | ||

| USB_RDY0 | C16 | O3 | USB_CLK | USB I/F FIFO read enable (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_RDY1 | C17 | O3 | USB_CLK | USB I/F FIFO write enable (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_RDY2 | B26 | O3 | USB_CLK | Reserved for future use (if not used, apply 10-kΩ pullup to 3.3 V) | ||

| USB_RSVD_14 | A15 | I3 | USB_CLK | Reserved for future use (if not used, apply 10-kΩ pulldown to DGND) | ||

| I2C_SCL | C25 | B2 | Master I2C clock - 400 kHz. Requires external pullup | |||

| I2C_SDA | D18 | B2 | I2C_SCL | Master I2C data - 400 kHz. Requires external pullup | ||

| EDID_I2C_SCL | F8 | B2 | HDMI EDID I2C clock. 400 kHz. Requires external pullup (if EDID is not used, must be pulled up to 3.3 V through a 47-kΩ resistor) | |||

| EDID_I2C_SDA | D6 | B2 | EDID_I2C_SCL | HDMI EDID I2C data. 400-kHz. Requires external pullup (if EDID is not used, must be pulled up to 3.3 V through a 47-kΩ resistor.) | ||

| SLAVE_SPI_CLK | B14 | I3 | Slave SPI clock | |||

| SLAVE_SPI_CS | C14 | I3 | SLAVE_SPI_CLK | Slave SPI chip select; weak pullup applied | ||

| SLAVE_SPI_MISO | D14 | O3 | SLAVE_SPI_CLK | Slave SPI data OUT (does not tristate) | ||

| SLAVE_SPI_MOSI | E14 | I3 | SLAVE_SPI_CLK | Slave SPI data IN; weak pullup applied | ||

| SLAVE_SPI_SOP | F21 | I3 | SLAVE_SPI_CLK | Reserved for future use | ||

| SLAVE_SPI_ACK | D20 | O3 | SLAVE_SPI_CLK | Slave SPI data busy | ||

| DMD INTERFACE | ||||||

| DMD_DAT_AP1 | AB27 | O4 | DMD_DCLK_AP, DMD_DCLK_AN | DMD data pins. LVDS pins for data bus A | ||

| DMD_DAT_AN1 | AB28 | O4 | ||||

| DMD_DAT_AP3 | Y25 | O4 | ||||

| DMD_DAT_AN3 | Y26 | O4 | ||||

| DMD_DAT_AP5 | W25 | O4 | ||||

| DMD_DAT_AN5 | W26 | O4 | ||||

| DMD_DAT_AP7 | W28 | O4 | ||||

| DMD_DAT_AN7 | W27 | O4 | ||||

| DMD_DAT_AP9 | V27 | O4 | ||||

| DMD_DAT_AN9 | V28 | O4 | ||||

| DMD_DAT_AP11 | V25 | O4 | ||||

| DMD_DAT_AN11 | V26 | O4 | ||||

| DMD_DAT_AP13 | V23 | O4 | ||||

| DMD_DAT_AN13 | V24 | O4 | ||||

| DMD_DAT_AP15 | T26 | O4 | ||||

| DMD_DAT_AN15 | U27 | O4 | ||||

| DMD_DCLK_AP | T25 | O4 | DMD data clock. LVDS clock for data bus A | |||

| DMD_DCLK_AN | U28 | O4 | DMD data clock. LVDS clock for data bus A | |||

| DMD_SCTRL_AP | R25 | O4 | DMD_DCLK_AP, DMD_DCLK_AN | DMD data serial-control signal bus A (LVDS) | ||

| DMD_SCTRL_AN | R26 | O | ||||

| DMD_DAT_BP1 | AC24 | O4 | DMD_DCLK_BP, DMD_DCLK_BN | DMD data pins. LVDS pins for data bus B | ||

| DMD_DAT_BN1 | AC25 | O4 | ||||

| DMD_DAT_BP3 | AC26 | O4 | ||||

| DMD_DAT_BN3 | AD26 | O4 | ||||

| DMD_DAT_BP5 | AE27 | O4 | ||||

| DMD_DAT_BN5 | AE28 | O4 | ||||

| DMD_DAT_BP7 | AD27 | O4 | ||||

| DMD_DAT_BN7 | AD28 | O4 | ||||

| DMD_DAT_BP9 | Y23 | O4 | ||||

| DMD_DAT_BN9 | Y24 | O4 | ||||

| DMD_DAT_BP11 | AC27 | O4 | ||||

| DMD_DAT_BN11 | AC28 | O4 | ||||

| DMD_DAT_BP13 | AB25 | O4 | ||||

| DMD_DAT_BN13 | AB26 | O4 | ||||

| DMD_DAT_BP15 | AA25 | O4 | ||||

| DMD_DAT_BN15 | AA26 | O4 | ||||

| DMD_DCLK_BP | U25 | O4 | DMD data clock. LVDS clock for data bus B | |||

| DMD_DCLK_BN | U26 | O4 | ||||

| DMD_SCTRL_BP | T21 | O4 | DMD_DCLK_AP, DMD_DCLK_AN | DMD data serial-control signal bus B (LVDS) | ||

| DMD_SCTRL_BN | T22 | O4 | ||||

| DMD_PWRDN | P26 | O3 | ASYNC | DMD power down (active-low) | ||

| RST_IRQ | M25 | I3 | ASYNC | DLPA200 interrupt (active-low) | ||

| RST_OE | M28 | O3 | ASYNC | DLPA200 output enable | ||

| RST_RST | H24 | O3 | ASYNC | DLPA200 reset | ||

| RST_STROBE | G28 | O3 | DLPA200 strobe | |||

| DMD INTERFACE (CONTINUED) | ||||||

| RST_SEL0 | G27 | O3 | RST_STROBE | DLPA200 voltage select | ||

| RST_SEL1 | G26 | |||||

| RST_MODE0 | L24 | O3 | RST_STROBE | DLPA200 mode select | ||

| RST_MODE1 | L23 | |||||

| RST_A0 | K25 | O3 | RST_STROBE | DLPA200 address | ||

| RST_A1 | J26 | |||||

| RST_A2 | J25 | |||||

| RST_A3 | K26 | |||||

| SCP_DMD_RST_DO | G25 | O3 | SCP_DMD_RST_CLK | SCP data out (write data) | ||

| SCP_DMD_RST_DI | H26 | I3 | SCP_DMD_RST_CLK | SCP data in (read data) | ||

| SCP_DMD_EN | L25 | O3 | SCP_DMD_RST_CLK | DMD SCP chip select | ||

| SCP_RST_EN | H23 | O3 | SCP_DMD_RST_CLK | DLPA200 SCP chip select | ||

| SCP_DMD_RST_CLK | H25 | O3 | DMD/DLPA200 SCP clock, 125 kHz | |||

| STATIC RAM INTERFACE | ||||||

| FLASH_CE | D12 | O3 | ASYNC | Flash chip enable | ||

| FLASH_SRAM_A0 | D13 | O3 | FLASH_SRAM_WE | Flash/SRAM address | ||

| FLASH_SRAM_A1 | A11 | |||||

| FLASH_SRAM_A2 | C11 | |||||

| FLASH_SRAM_A3 | D11 | |||||

| FLASH_SRAM_A4 | A12 | |||||

| FLASH_SRAM_A5 | B12 | |||||

| FLASH_SRAM_A6 | D10 | |||||

| FLASH_SRAM_A7 | A10 | |||||

| FLASH_SRAM_A8 | B10 | |||||

| FLASH_SRAM_A9 | B8 | |||||

| FLASH_SRAM_A10 | C8 | |||||

| FLASH_SRAM_A11 | A7 | |||||

| FLASH_SRAM_A12 | B7 | |||||

| FLASH_SRAM_A13 | A4 | |||||

| FLASH_SRAM_A14 | D7 | |||||

| FLASH_SRAM_A15 | C6 | |||||

| FLASH_SRAM_A16 | D8 | |||||

| FLASH_SRAM_A17 | B6 | |||||

| FLASH_SRAM_A18 | C7 | |||||

| FLASH_SRAM_A19 | A8 | |||||

| FLASH_SRAM_A20 | C4 | |||||

| FLASH_SRAM_A21 | B3 | |||||

| FLASH_SRAM_A22 | A3 | |||||

| FLASH_SRAM_A23 | C5 | |||||

| FLASH_SRAM_A24 | D5 | |||||

| FLASH_SRAM_A25 | B4 | |||||

| FLASH_SRAM_A26 | D4 | |||||

| STATIC RAM INTERFACE (CONTINUED) | ||||||

| FLASH_SRAM_D0 | E11 | B2 | FLASH_SRAM_WE | Flash/SRAM data | ||

| FLASH_SRAM_D1 | F10 | |||||

| FLASH_SRAM_D2 | E10 | |||||

| FLASH_SRAM_D3 | G9 | |||||

| FLASH_SRAM_D4 | E8 | |||||

| FLASH_SRAM_D5 | E7 | |||||

| FLASH_SRAM_D6 | E5 | |||||

| FLASH_SRAM_D7 | E4 | |||||

| FLASH_SRAM_D8 | F11 | |||||

| FLASH_SRAM_D9 | E12 | |||||

| FLASH_SRAM_D10 | F12 | |||||

| FLASH_SRAM_D11 | G12 | |||||

| FLASH_SRAM_D12 | G13 | |||||

| FLASH_SRAM_D13 | H13 | |||||

| FLASH_SRAM_D14 | F14 | |||||

| FLASH_SRAM_D15 | G14 | |||||

| FLASH_SRAM_OE | C10 | O3 | Flash output enable | |||

| FLASH_SRAM_RDY | C13 | I3 | Flash wait | |||

| FLASH_SRAM_RST | C12 | O3 | Flash reset | |||

| FLASH_SRAM_WE | A6 | O3 | Flash write enable | |||

| SRAM_CE | B11 | O3 | SRAM chip enable | |||

| SRAM_LB | D9 | O3 | SRAM lower byte enable | |||

| SRAM_UB | C9 | O3 | SRAM upper byte enable | |||

| SDRAM INTERFACE | ||||||

| MEM_CLK_P0 | R2 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_N0 | R1 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_P1 | U3 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_N1 | U4 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_P2 | AC5 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_N2 | AC4 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_P3 | AE14 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CLK_N3 | AF14 | O5 | DDR2 memory, differential memory clock | |||

| MEM_CKE0 | AF12 | O5 | ||||

| MEM_BA0 | Y19 | O5 | MEM_CLK | |||

| MEM_BA1 | AD21 | O5 | MEM_CLK | |||

| MEM_BA2 | AE7 | O5 | MEM_CLK | |||

| SDRAM INTERFACE (CONTINUED) | ||||||

| MEM_A0 | AD24 | O5 | MEM_CLK | DDR2 memory, multiplexed row and column address. The memory in the kit is 512 Mb in ×16 mode, 8 Meg × 16 bits × 4 banks. Only A(12:0) and BA(1:0) are currently used. A(15:13) and BA(2) are reserved for future use (RFU). | ||

| MEM_A1 | AF21 | |||||

| MEM_A2 | AG23 | |||||

| MEM_A3 | AE8 | |||||

| MEM_A4 | AG12 | |||||

| MEM_A5 | AF23 | |||||

| MEM_A6 | AC17 | |||||

| MEM_A7 | AA16 | |||||

| MEM_A8 | AE23 | |||||

| MEM_A9 | AE22 | |||||

| MEM_A10 | AE16 | |||||

| MEM_A11 | AD25 | |||||

| MEM_A12 | AF19 | |||||

| MEM_A13 | AH10 | |||||

| MEM_A14 | AA8 | |||||

| MEM_A15 | AD11 | |||||

| MEM_CAS | AG19 | O5 | MEM_CLK | Column address strobe, active low | ||

| MEM_RAS | AE20 | O5 | MEM_CLK | Row address strobe, active low | ||

| MEM_CS0 | AF13 | O5 | MEM_CLK | Chip select, active low | ||

| MEM_WE | AG25 | O5 | MEM_CLK | Write enable, active low | ||

| MEM_ODT | AH12 | O5 | MEM_CLK | |||

| MEM_DM0 | W2 | O5 | MEM_CLK | |||

| MEM_DM1 | AE2 | O5 | MEM_CLK | |||

| MEM_DM2 | AH6 | O5 | MEM_CLK | |||

| MEM_DM3 | AF7 | O5 | MEM_CLK | |||

| MEM_DM4 | AE13 | O5 | MEM_CLK | |||

| MEM_DM5 | AH18 | O5 | MEM_CLK | |||

| MEM_DM6 | AF24 | O5 | MEM_CLK | |||

| MEM_DM7 | AG26 | O5 | MEM_CLK | |||

| MEM_DS0 | AB2 | B1 | MEM_CLK_P0 | |||

| MEM_DS1 | AE3 | B1 | MEM_CLK_N0 | |||

| MEM_DS2 | AD7 | B1 | MEM_CLK_P1 | |||

| MEM_DS3 | AE10 | B1 | MEM_CLK_N1 | |||

| MEM_DS4 | AF11 | B1 | MEM_CLK_P2 | |||

| MEM_DS5 | AF17 | B1 | MEM_CLK_N2 | |||

| MEM_DS6 | AE18 | B1 | MEM_CLK_P3 | |||

| MEM_DS7 | AF26 | B1 | MEM_CLK_N3 | |||

| SDRAM INTERFACE (CONTINUED) | ||||||

| MEM_D0 | R3 | B1 | MEM_DS0, MEM_DS1 | |||

| MEM_D1 | R4 | B1 | ||||

| MEM_D2 | T4 | B1 | ||||

| MEM_D3 | R5 | B1 | ||||

| MEM_D4 | U1 | B1 | ||||

| MEM_D5 | V4 | B1 | ||||

| MEM_D6 | V2 | B1 | ||||

| MEM_D7 | V1 | B1 | ||||

| MEM_D8 | U6 | B1 | ||||

| MEM_D9 | Y4 | B1 | ||||

| MEM_D10 | AC2 | B1 | ||||

| MEM_D11 | AC1 | B1 | ||||

| MEM_D12 | AC3 | B1 | ||||

| MEM_D13 | AD2 | B1 | ||||

| MEM_D14 | AB3 | B1 | ||||

| MEM_D15 | AA4 | B1 | ||||

| MEM_D16 | AE6 | B1 | MEM_DS2, MEM_DS3 | |||

| MEM_D17 | AF4 | B1 | ||||

| MEM_D18 | AG3 | B1 | ||||

| MEM_D19 | AH3 | B1 | ||||

| MEM_D20 | AF6 | B1 | ||||

| MEM_D21 | AH4 | B1 | ||||

| MEM_D22 | AD8 | B1 | ||||

| MEM_D23 | AG6 | B1 | ||||

| MEM_D24 | AB9 | B1 | ||||

| MEM_D25 | AD10 | B1 | ||||

| MEM_D26 | AG7 | B1 | ||||

| MEM_D27 | AH7 | B1 | ||||

| MEM_D28 | AC8 | B1 | ||||

| MEM_D29 | AA10 | B1 | ||||

| MEM_D30 | AG8 | B1 | ||||

| MEM_D31 | AH8 | B1 | ||||

| SDRAM INTERFACE (CONTINUED) | ||||||

| MEM_D32 | AF8 | B1 | MEM_DS4, MEM_DS5 | |||

| MEM_D33 | AE9 | B1 | ||||

| MEM_D34 | AF10 | B1 | ||||

| MEM_D35 | AG10 | B1 | ||||

| MEM_D36 | AE12 | B1 | ||||

| MEM_D37 | AE11 | B1 | ||||

| MEM_D38 | AG11 | B1 | ||||

| MEM_D39 | AH11 | B1 | ||||

| MEM_D40 | AC15 | B1 | ||||

| MEM_D41 | AF15 | B1 | ||||

| MEM_D42 | AG17 | B1 | ||||

| MEM_D43 | AH17 | B1 | ||||

| MEM_D44 | AF16 | B1 | ||||

| MEM_D45 | AB16 | B1 | ||||

| MEM_D46 | AE17 | B1 | ||||

| MEM_D47 | AG18 | B1 | ||||

| MEM_D48 | AH19 | B1 | MEM_DS6, MEM_DS7 | |||

| MEM_D49 | AD17 | B1 | ||||

| MEM_D50 | AG21 | B1 | ||||

| MEM_D51 | AH21 | B1 | ||||

| MEM_D52 | AG22 | B1 | ||||

| MEM_D53 | AH22 | B1 | ||||

| MEM_D54 | AH23 | B1 | ||||

| MEM_D55 | AE19 | B1 | ||||

| MEM_D56 | AF25 | B1 | ||||

| MEM_D57 | AF20 | B1 | ||||

| MEM_D58 | AD18 | B1 | ||||

| MEM_D59 | AE21 | B1 | ||||

| MEM_D60 | AE25 | B1 | ||||

| MEM_D61 | AH25 | B1 | ||||

| MEM_D62 | AF22 | B1 | ||||

| MEM_D63 | AE24 | B1 | ||||

| LED DRIVER INTERFACE | ||||||

| PWM0 | C27 | O3 | Async | PWM signal used to control the LED current (if not used, apply 10-kΩ pulldown to DGND) | ||

| PWM1 | D28 | O3 | Async | PWM signal used to control the LED current (if not used, apply 10-kΩ pulldown to DGND) | ||

| PWM2 | D27 | O3 | Async | PWM signal used to control the LED current (if not used, apply 10-kΩ pulldown to DGND) | ||

| PWM3 | D26 | O3 | Async | PWM signal used to control the LED current (if not used, apply 10-kΩ pulldown to DGND) | ||

| LED_IR_EN | E28 | O3 | Async | IR LED enable strobe. Controlled by programmable DMD sequence timing (active high), (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_RED_EN | F28 | O3 | Async | RED LED enable strobe. Controlled by programmable DMD sequence timing (active high), (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_GRN_EN | E27 | O3 | Async | Green LED enable strobe. Controlled by programmable DMD sequence timing (active high), (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_BLU_EN | F27 | O3 | Async | Blue LED enable strobe. Controlled by programmable DMD sequence timing (active high), (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_SUBFRAME | E26 | O3 | Async | Subframe signal used by LED driver. Controlled by programmable DMD sequence timing (active high), (if not used, apply 1-kΩ pulldown to DGND) | ||

| SYNC_0 | F26 | O3 | Async | Extra strobe. Controlled by programmable DMD sequence timing (active-high) | ||

| SYNC_1 | F25 | O3 | Async | Extra strobe. Controlled by programmable DMD sequence timing (active-high) | ||

| SYNC_2 | F24 | O3 | Async | Extra strobe. Controlled by programmable DMD sequence timing (active-high) | ||

| LED_EN | L28 | O3 | Async | LED driver enable. Active-low output control to external LED drive logic, recommend 1-kΩ pullup to 3.3 V | ||

| LED_SYNC | M21 | O3 | Async | Reserved for future use; weak pullup applied | ||

| LED_SYNCEN | C24 | O3 | Async | Inverted LED_LIT signal (if not used, apply 10-kΩ pulldown to DGND) | ||

| LED_LIT | J28 | I3 | Async | LED driver status, (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_SENS | K27 | I3 | Async | Reserved for future use (if not used, apply 1-kΩ pulldown to DGND) | ||

| LED_SPI_CLK | N26 | O3 | Async | LED SPI master clock (if not used, apply 1-kΩ pullup to 3.3 V) | ||

| LED_SPI_CS | M26 | O3 | LED_SPI_CLK | LED SPI master chip select (if not used, apply 1-kΩ pullup to 3.3 V) | ||

| LED_SPI_DIR | P25 | O3 | LED_SPI_CLK | LED SPI master driver direction (if not used, apply 1-kΩ pullup to 3.3 V) | ||

| LED_SPI_MISO | L27 | I3 | LED_SPI_CLK | LED SPI master data IN (if not used, apply 1-kΩ pullup to 3.3 V) | ||

| LED_SPI_MOSI | L26 | O3 | LED_SPI_CLK | LED SPI master data OUT; weak pullup applied | ||

| SYSTEM INTERFACES | ||||||

| CFG_CSO | E2 | O3 | CFG_DCLK | Chip-select output for an external serial configuration device. Active low | ||

| CFG_CLK | P3 | O3 | CFG_DCLK | Configuration serial EPROM data clock | ||

| CFG_ASDI | N7 | I3 | CFG_DCLK | Data input from an external serial configuration device. Provides configuration data for the device | ||

| CFG_ASDO | F4 | O3 | CFG_DCLK | Serial data output. This pin sends address and control information to the external PROM during configuration. | ||

| CFG_STATUS | M6 | O3 | CFG_DCLK | Configuration status pin | ||

| CFG_DONE | P24 | O3 | CFG_DCLK | Configuration-done status pin. Signal goes high at the end of configuration. | ||

| CFG_MSEL0 | N22 | I3 | Async | Configuration-mode selection signals | ||

| CFG_MSEL1 | P23 | |||||

| CFG_MSEL2 | M22 | |||||

| CFG_MSEL3 | P22 | |||||

| CFG_CE | R8 | I3 | Async | Chip enable. Active-low | ||

| CFG_EN | P4 | I3 | Async | Configuration control. Configuration starts when a low-to-high transition is detected at this pin. | ||

| CFG_CEO | P28 | O3 | Async | |||

| REF_CLK | J27 | I3 | 50-MHz reference clock, 3.3 V | |||

| RESET | A14 | I3 | Async | Device reset (active-low) | ||

| PWR_GOOD | A23 | I3 | Async | System power-good indicator | ||

| RESERVED | ||||||

| RSVD_H10 | N4 | B2 | GPIO | |||

| RSVD_H11 | L2 | B2 | GPIO | |||

| RSVD_H12 | K4 | B2 | GPIO | |||

| RSVD_H6 | G1 | B2 | GPIO | |||

| RSVD_H5 | G5 | B2 | GPIO | |||

| RSVD_H4 | G6 | B2 | GPIO | |||

| RSVD_H2 | E1 | B2 | GPIO | |||

| RSVD_H1 | C2 | B2 | GPIO | |||

| RSVD_T0 | E22 | These I/Os can be left open or unconnected for normal operation. | ||||

| RSVD_T1 | D21 | |||||

| RSVD_T2 | A21 | |||||

| RSVD_T3 | C18 | |||||

| RSVD_T4 | B22 | |||||

| RSVD_T5 | B21 | |||||

| RSVD_T6 | D17 | |||||

| RSVD_T7 | E21 | |||||

| RSVD_TC | M24 | |||||

| RSVD_D0 | A17 | I3 | Reserved for future use, do not connect | |||

| RSVD_D1 | D15 | O3 | Reserved for future use, do not connect | |||

| RSVD_D2 | E17 | I3 | Reserved for future use, do not connect | |||

| RSVD_D3 | F15 | O3 | Reserved for future use, do not connect | |||

| RSVD_H3 | E3 | I3 | Reserved for future use, can be left open, recommend grounding | |||

| RSVD_H7 | H7 | I3 | Reserved for future use, can be left open, recommend grounding | |||

| RSVD_H8 | L5 | I3 | Reserved for future use, can be left open, recommend grounding | |||

| RSVD_H9 | M5 | I3 | Reserved for future use, can be left open, recommend grounding | |||

| RESERVED (CONTINUED) | ||||||

| RSVD_H13 | J1 | I3 | Reserved for future use, can be left open, recommend grounding | |||

| RSVD_P0 | P7 | I4 | Reserved for future use, do not connect | |||

| RSVD_P1 | P6 | O2 | Reserved for future use, do not connect | |||

| RSVD_P2 | P8 | I4 | Reserved for future use, do not connect | |||

| RSVD_P3 | P5 | I4 | Reserved for future use, do not connect | |||

| RSVD_G0 | C23 | O3 | Reserved for future use, do not connect | |||

| RSVD_G1 | F19 | O3 | Reserved for future use, do not connect | |||

| RSVD_G2 | M27 | O3 | Reserved for future use, do not connect | |||

| RSVD_G3 | N21 | O3 | Reserved for future use, do not connect | |||

| RSVD_G4 | P27 | O3 | Reserved for future use, do not connect | |||

| RSVD_G5 | A18 | O3 | Reserved for future use, do not connect | |||

| RSVD_G6 | A19 | O3 | Reserved for future use, do not connect | |||

| RSVD_S1 | AG14 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_S2 | AG15 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_S3 | AH14 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_X11 | AH15 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_S20 | Y27 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_S21 | Y28 | Unused input only, can be left open, recommend 10-kΩ pulldown to DGND | ||||

| RSVD_X9 | AA22 | Reserved for future use, do not connect | ||||

| RSVD_S0 | AA24 | Reserved for future use, can be left open, recommend 10-kΩ pullup to 2.5 V | ||||

| RSVD_X10 | AB23 | Reserved for future use, do not connect | ||||

| RSVD_X6 | AB24 | Reserved for future use, do not connect | ||||

| RSVD_X3 | AC21 | Reserved for future use, do not connect | ||||

| RSVD_X15 | AA17 | Reserved, do not leave open, required: 49.4-Ω pullup to 1.8 V | ||||

| RSVD_X14 | AB17 | Reserved, do not leave open, required: 49.9-Ω pulldown to DGND | ||||

| RSVD_X13 | U7 | Reserved, do not leave open, required: 49.4-Ω pullup to 1.8V | ||||

| RSVD_X12 | U8 | Reserved, do not leave open, required: 49.9-Ω pulldown to DGND | ||||

| RSVD_X2 | AE15 | Reserved for future use, do not connect | ||||

| RSVD_X0 | AF18 | Reserved for future use, do not connect | ||||

| RSVD_X1 | AD15 | Reserved for future use, do not connect | ||||

| RSVD_X8 | AF27 | Reserved for future use, do not connect | ||||

| RSVD_X4 | AF9 | Reserved for future use, do not connect | ||||

| RSVD_S4 | AH26 | Reserved for future use, can be left open, recommend 10-kΩ pullup to 1.8 V | ||||

| RSVD_S5 | B25 | Reserved for future use, do not connect | ||||

| RSVD_S6 | C20 | Reserved for future use, do not connect | ||||

| RSVD_S8 | D19 | Reserved for future use, do not connect | ||||

| RSVD_X5 | E24 | Reserved for future use, do not connect | ||||

| RSVD_S10 | F22 | Reserved for future use, do not connect | ||||

| RESERVED (CONTINUED) | ||||||

| RSVD_S11 | K28 | Reserved for future use, do not connect | ||||

| RSVD_S14 | N25 | Reserved for future use, do not connect | ||||

| RSVD_X7 | R24 | Reserved for future use, do not connect | ||||

| RSVD_S16 | R27 | Reserved for future use, do not connect | ||||

| RSVD_S17 | R28 | Reserved for future use, do not connect | ||||

| RSVD_S18 | U23 | Reserved for future use, can be left open, recommend 10-kΩ pullup to 2.5 V | ||||

| RSVD_S19 | U24 | Reserved for future use, can be left open, recommend 10-kΩ pullup to 2.5 V | ||||

| POWER AND GROUND(3) | ||||||

| P1P2V | PWR | N/A | 1.2-V core power | |||

| P2P5V_DPLL | PWR | N/A | 2.5-V filtered power for internal PLL | |||

| P1P8V | PWR | N/A | 1.8-V I/O power | |||

| P2P5V | PWR | N/A | 2.5-V I/O power | |||

| P3P3V | PWR | N/A | 3.3-V I/O power | |||

| GND | PWR | N/A | Common digital ground | |||

| GNDA | PWR | N/A | Common PLL ground | |||

(1) See I/O Electrical Characteristics for more detail.

(2) 24-bit data is mapped according to RGB888 pixel format. See Figure 13.

(3) Unused inputs should be pulled down to ground through an external resistor.

Power and Ground Pins

| PIN | DESCRIPTION | |

|---|---|---|

| NAME | NUMBER | |

| INPUT POWER AND GROUND PINS | ||

| VCC_1P2V | K9, K11, K13, K15, K17, K19, L10, L12, L14, L16, L18, L20, M9, M11, M13, M15, M17, M19, N10, N12, N14, N16, N18, N20, P9, P11, P13, P15, P17, P19, R10, R12, R14, R16, R18, R20, T9, T11, T13, T15, T17, T19, U10, U12, U14, U16, U18, U20, V9, V11, V13, V15, V17, V19, W10, W12, W14, W16, W18, W20 | 1.2-V power supply for core logic |

| VCC_2P5V | AA28, AG28, T24, T28, W24 | 2.5-V power supply for I/Os on bank 5 |

| VCC_1P8V | AA1, AG1, T1, T5, W5, AA11, AD6, AD9, AD13, AH2, AH5, AH9, AH13, AA18, AD16, AD20, AD23, AH16, AH20, AH24, AH27 | 1.8-V power supply for I/Os on banks 2, 3, 4 |

| VCC_3P3V | B1, H1, K5, N1, N5, B28, H28, K24, N24, N28 A16, A20, A24, A27, E16, E20, E23, H18, A2, A5, A9, A13, E6, E9, E13, H11 | 3.3-V power supply for I/Os on banks 1, 6, 7, 8 |

| VCCA | Y8, J21, J8, Y21 | 2.5-V power supply for the internal PLL analog supply |

| VCCD_PLL | Y9, J20, J9, Y20 | 1.2-V power supply for the internal PLL digital supply |

| VREF_B2 | T7, T8, AB4 | DDR2 VREF 0.9 V. The SDRAM specification provides guidelines on how these references should be connected. It is not just any 0.9-V source on the board. |

| VREF_B3 | AB13, AB11, Y10 | DDR2 VREF 0.9 V. The SDRAM specification provides guidelines on how these references should be connected. It is not just any 0.9-V source on the board. |

| VREF_B4 | AB20, AC18, AA15 | DDR2 VREF 0.9 V. The SDRAM specification provides guidelines on how these references should be connected. It is not just any 0.9-V source on the board. |

| DGND | K10, K12, K14, K16, K18, K20, L9, L11, L13, L15, L17, L19, M10, M12, M14, M16, M18, M20, N9, N11, N13, N15, N17, N19, P10, P12, P14, P16, P18, P20, R9, R11, R13, R15, R17, R19, T10, T12, T14, T16, T18, T20, U9, U11, U13, U15, U17, U19, V10, V12, V14, V16, V18, V20, W9, W11, W13, W15, W17, W19, AA2, AA27, AC6, AC9, AC13, AC16, AC20, AC23, AF1, AF28, AG2, AG5, AG9, AG13, AG16, AG20, AG24, AG27, B2, B5, B9, B13, B16, B20, B24, B27, C1, C28, F6, F9, F13, F16, F20, F23, H2, H27, J11, J18, K6, K23, N2, N6, N23, N27, T2, T6, T23, T27, W6, W23, Y11, Y18 | Common ground |

| DGND2 | H9, H20, AA9, AA20 | Analog ground return for the PLL (This should not be connected to the common ground GND.) |

| NC | C3, F7, G7, G8, G10, G11, G19, G20, G21, G22, G23, G24, H8, H10, H12, H14, H15, H16, H17, H19, H21, H22, J5, J6, J7, J10, J12, J13, J14, J15, J16, J17, J19, J23, J24, K7, K8, K21, K22, L6, L7, L8, L21, L22, M7, M8, M23, N8, P21, R7, R21, R22, R23, U21, U22, V5, V6, V7, V8, V21, V22, W4, W7, W8, W21, W22, Y5, Y6, Y7, Y12, Y13, Y14, Y15, Y16, Y17, Y22, AA5, AA6, AA7, AA12, AA13, AA14, AA19, AA21, AA23, AB10, AB12, AB14, AB15, AB18, AB19, AB21, AB22, AC10, AC12, AC14, AC19, AC22, AD14, AD19, AD22, AE26 | No-connect pins |