JAJSGA8F september 2018 – february 2023 TPS1663

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Hot Plug-In and In-Rush Current Control

- 9.3.2 Undervoltage Lockout (UVLO)

- 9.3.3 Overvoltage Protection (OVP)

- 9.3.4 Overload and Short Circuit Protection

- 9.3.5 Output Power Limiting, PLIM (TPS16632 Only)

- 9.3.6 Current Monitoring Output (IMON)

- 9.3.7 FAULT Response (FLT)

- 9.3.8 Power Good Output (PGOOD)

- 9.3.9 IN, P_IN, OUT and GND Pins

- 9.3.10 Thermal Shutdown

- 9.3.11 Low Current Shutdown Control (SHDN)

- 9.4 Device Functional Modes

- 10Application and Implementation

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RGE|24

- PWP|20

サーマルパッド・メカニカル・データ

発注情報

3 概要

TPS1663x は、31mΩ の FET を内蔵した使いやすい正の 60V / 6A の eFuse です。負荷、ソース、および eFuse 自体の保護に加え、正確な過電流保護、高速の短絡保護、出力スルーレート制御、過電圧保護、低電圧誤動作防止などの調整可能な機能を備えています。TPS16332 デバイスは、IEC61010-1 や UL1310 などの規格に簡単に準拠できるようにする調整可能な出力電力制限 (PLIM) 機能を備えています。本デバイスは、調整可能な過電流保護機能も内蔵しています。PGOOD を使用して、下流の DC / DC コンバータの制御をイネーブル / ディセーブルできます。

シャットダウン・ピンにより、内蔵 FET のイネーブル / ディセーブルを外部的に制御でき、デバイスを低電流のシャットダウン・モードに移行させることもできます。システム状態の監視や下流負荷の制御のために、このデバイスはフォルト出力および高精度の電流監視出力を備えています。MODE ピンにより、2 種類の電流制限フォルト応答 (ラッチオフ、自動再試行) のどちらにもデバイスを柔軟に設定できます。

これらのデバイスは 4mm × 4mm の 24 ピン VQFN パッケージで供給され、-40°C~+125°C の温度範囲で動作が規定されています。

パッケージ情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| TPS16630 TPS16632 |

VQFN (24) | 4.00mm × 4.00mm |

| TPS16630 | HTSSOP (20) | 6.50mm × 4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

簡略回路図

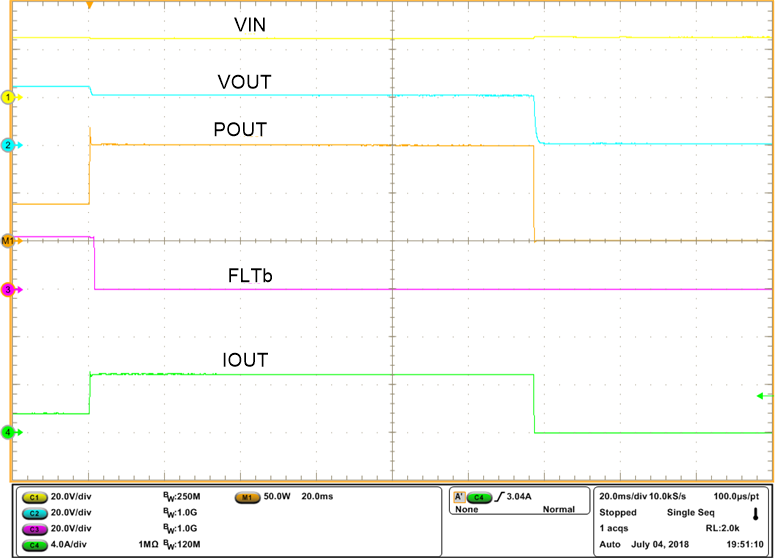

簡略回路図 TPS16632 の出力電力制限性能

TPS16632 の出力電力制限性能