SPRADF4 December 2023 TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28P650DK

5.2 Hardware-Based Scheme

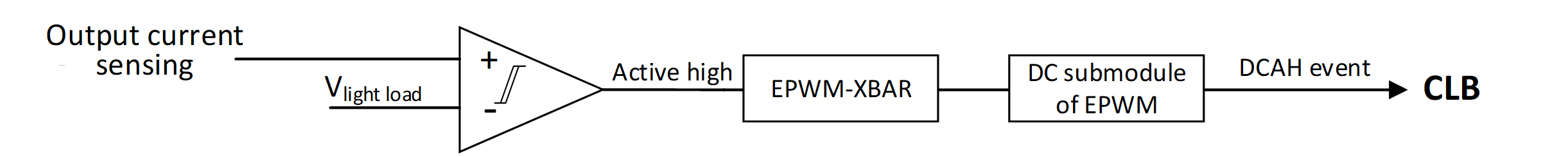

The following suggested hardware-based scheme achieves faster control response for SR PWM. The digital compare (DC) events created by the DC submodule of EPWM are included to help create a link between the CMPSS and the CLB module among multiple input signals for CLB. Figure 4-2 shows that the output current signal is fed into the CMPSS and that Vlight_load refers to the load current threshold for turning SR PWM on or off. Figure 2-3 shows the DCAH event selected as the input signal IN5 for CLB2. The DCAH event changes to logic 1 when the load increase is larger than the load threshold set by Vlight_load, with the active-high logic from the CMPSS output. The SR PWM is turned on as long as the load changes from light load to heavy load. Figure 4-2 shows example codes for the CMPSS used for the SR on and off control.

Figure 5-1 Hardware-Based SR Control with

Load Current Sensing

Figure 5-1 Hardware-Based SR Control with

Load Current SensingXBAR_setEPWMMuxConfig(XBAR_TRIP10,XBAR_EPWM_MUX02_CMPSS2_CTRIPH);

XBAR_enableEPWMMux(XBAR_TRIP10, XBAR_MUX02);

// Enable CMPSS2 and configure the negative input signal to come from the DAC

//

CMPSS_enableModule(CMPSS2_BASE);

CMPSS_configHighComparator(CMPSS2_BASE, CMPSS_INSRC_DAC);

// Set DAC reference level, refers to 6A

//

CMPSS_setDACValueHigh(CMPSS2_BASE, 112);

CMPSS_configDAC(CMPSS2_BASE, CMPSS_DACREF_VDDA);

// Enable the digital filter

CMPSS_configFilterHigh(CMPSS2_BASE,1,150,149);

CMPSS_initFilterHigh(CMPSS2_BASE);

CMPSS_configOutputsHigh(CMPSS2_BASE, CMPSS_TRIP_FILTER);

CMPSS_setHysteresis(CMPSS2_BASE,4);

EPWM_selectDigitalCompareTripInput(EPWM2_BASE,

EPWM_DC_TRIP_TRIPIN10,

EPWM_DC_TYPE_DCAH);