SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

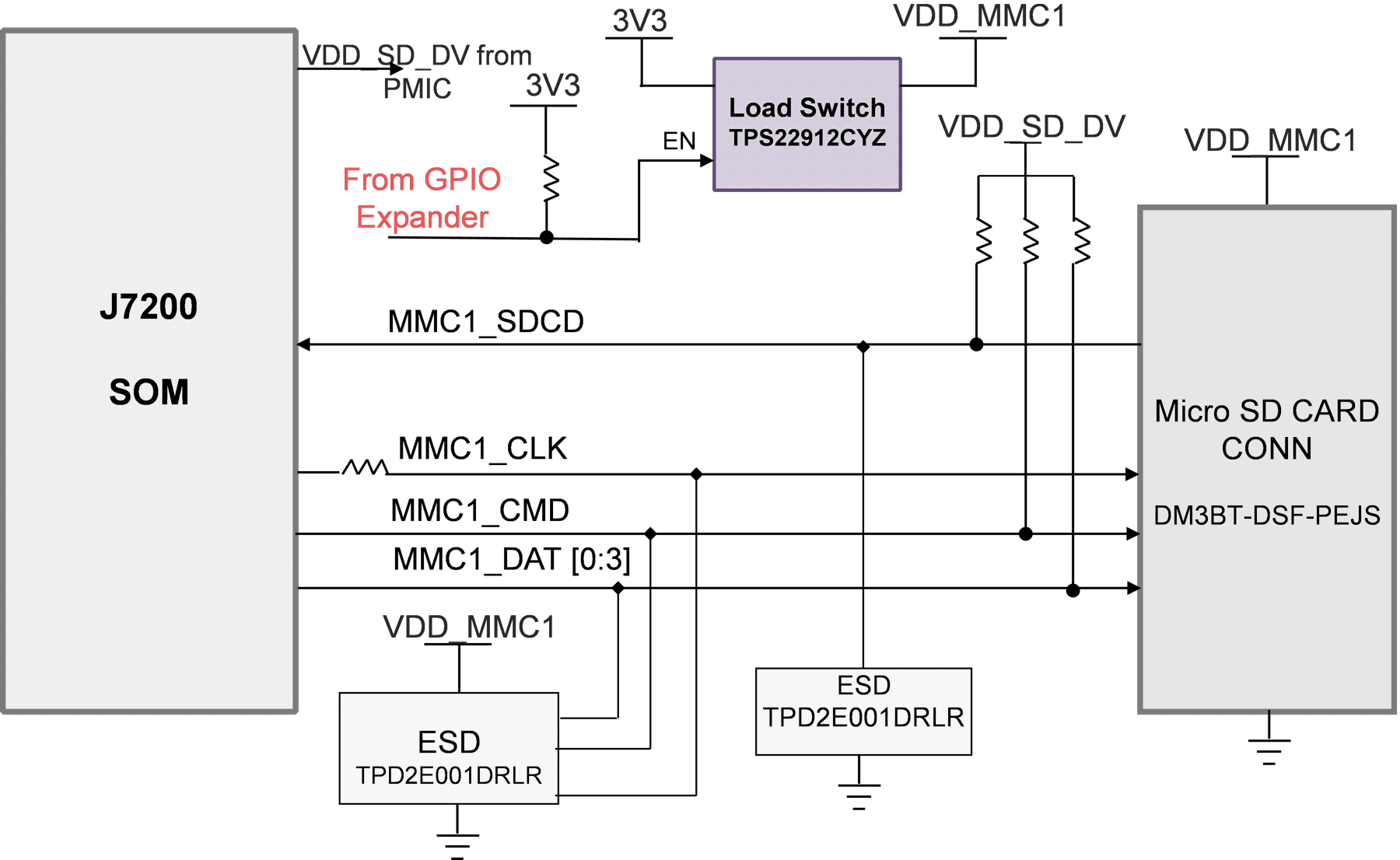

4.8.3.2 MMC1 – Micro SD Interface

The EVM supports a Micro SD card interface connected to MMC1 port of SoC. The Micro SD card socket Mfr. Part# DM3BT-DSF-PEJS is interfaced with MMC1 port of SoC. This supports UHS1 operation including IO operations at both 1.8 V and 3.3 V. The Micro SD card interface is set to operate in SD mode by default.

The IO voltage for the MMC1 port is derived from the discrete LDO (TLV7103318), which is controlled by SEL_SDIO_3V3_1V8n (GPIO0_55). The SD Card power is provided using a load switch, which is controlled by a GPIO from IO expander. Control signal “GPIO_uSD_PWR_EN” is driven by the I2C IO expander U31 Port02 on the CP board. This IO expander is controlled by the processor’s I2C0 port. I2C address of the IO expander is 0x22.

Figure 4-14 Micro-SD Card Block

Diagram

Figure 4-14 Micro-SD Card Block

DiagramAn ESD protection device Mfr. Part# TPD2E001DRLRis provided for data, clock, command and card detect signals. The CD (card detect) pin of Micro SD card socket is pulled high and connected to CD pin of SoC. An external pull up resistor (47K) is provided on data [3:0] and CMD signals to avoid floating.