SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

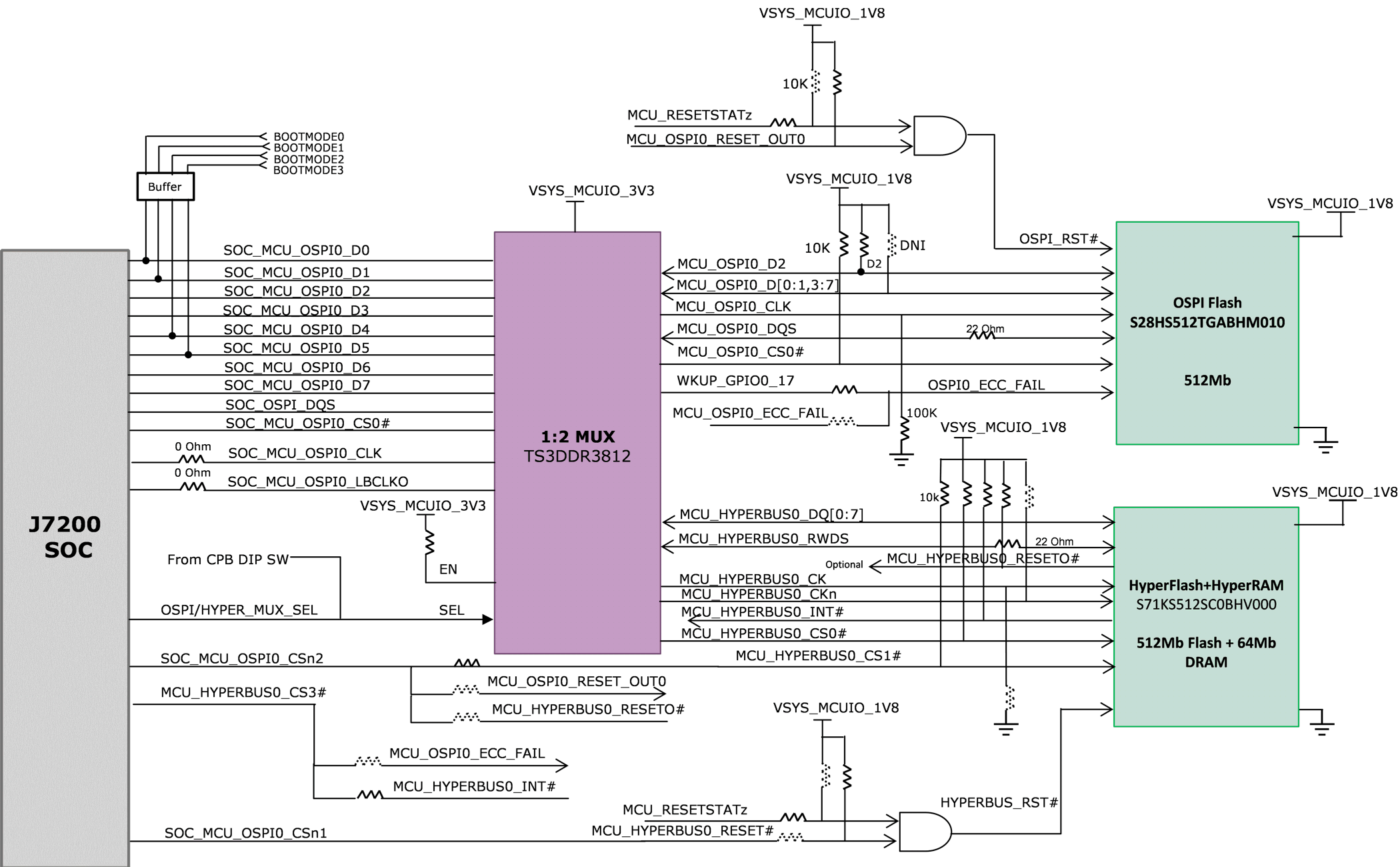

4.8.2 OSPI Interface

The J7200 SOM has 512-Mbit OSPI memory device of part number S28HS512TGABHM010 connected to OSPI0 interface of J7200 processor. The OSPI interface supports single and double data rates with memory speed up to 166 MHz SDR and 200 MHz DDR.

J7200 SOM is xSPI compliant, specifically JEDEC eXpanded SPI (JESD251) compliant.

The SOM board also supports an option to include Hyper Flash + Hyper RAM Mfr. Part# S71KS512SC0, which is a 512Mb flash + 64Mb DRAM. 12-bit Active mux TS3DDR3812RUAR is provided to select either OSPI or HBMC interface. The selection of OSPI and hyper flash will be done by using a DIP (SW3) switch which is populated on the CP board. For more details, see Section 3.4.1.

Figure 4-12 J7200 SoM OSPI and Hyper

Flash

Figure 4-12 J7200 SoM OSPI and Hyper

Flash