SPRUJ91A april 2023 – may 2023 AM68 , AM68 , AM68A , AM68A , TDA4AL-Q1 , TDA4AL-Q1 , TDA4VE-Q1 , TDA4VE-Q1 , TDA4VL-Q1 , TDA4VL-Q1

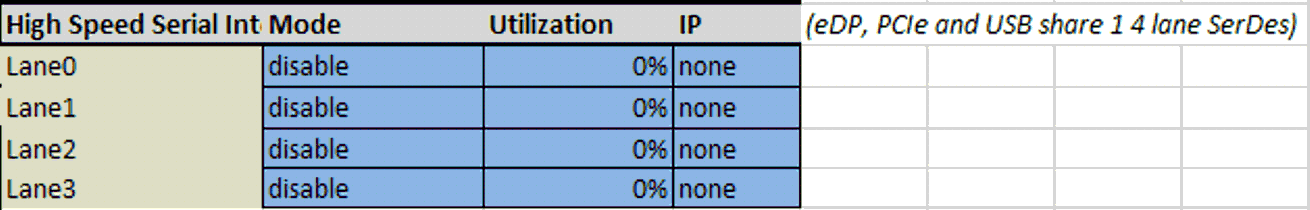

3.5 High Speed Serial Interface

There is one high speed serializing / deserializing (SerDes) interface on this device. The SerDes has 4 lanes for which the mode, utilization and IP is selected.

Note: The loading for the core portion of the IP is determined

based upon the selected IP. The user defines what IP is driving the various lanes of

the SerDes.