DLPU040B October 2016 – March 2023 DLP650LNIR , DLPC410

- DLP Discovery 4100 Development Platform User’s Guide

- Trademarks

- 1Introduction

-

2Overview

- 2.1 The DLP Discovery 4100 Development Platform

- 2.2 DLP Discovery 4100 Development Platform Photo

- 2.3

Key Components

- 2.3.1 Xilinx Virtex 5 APPSFPGA

- 2.3.2 DLPC410 - Digital Controller for DLP Discovery 4100 Chipset

- 2.3.3 DLPA200 - DMD Micromirror Driver

- 2.3.4 DLPR410 - Configuration PROM for DLPC410 Controller

- 2.3.5 APPSFPGA Flash Configuration PROM

- 2.3.6 DMD Connectors

- 2.3.7 USB Controller

- 2.3.8 50-MHz Oscillator

- 2.3.9 DDR2 SODIMM Connector

- 2.3.10 Connectors

- 2.3.11 Battery

- 2.3.12 Power Supplies

-

3Hardware Overview and Setup

- 3.1 Getting Started

- 3.2

User Connectors and I/O

- 3.2.1 J12 Input Power Connector

- 3.2.2 J18 Input Power Connector

- 3.2.3 J1 USB Connector Pinout

- 3.2.4 J3 USB GPIO

- 3.2.5 J6 GPIO_A Connector

- 3.2.6 J8 DLPC410 Mictor Connector

- 3.2.7 J9 USB/APPSFPGA Mictor Connector

- 3.2.8 J13 DMD Flex 1 Connector

- 3.2.9 J14 DMD Flex 2 Connector

- 3.2.10 J15 DDR2 SODIMM Connector

- 3.2.11 J16, J17 EXP Connectors

- 3.2.12 H1 Xilinx FPGA JTAG Header

- 3.3 Configuration Jumpers

- 3.4 Switches

- 3.5 Power and Status LEDs

- 3.6 Test Points

-

4Software

- 4.1 Overview

- 4.2 DLP Discovery 4100 Operation

- 4.3 Graphical User Interface

- 4.4 Script and Status Operations

- 4.5 DLPC410 Control Window

- 4.6 Test Patterns Window

- 4.7 About Box

- 4.8 Links

- 5Related Documentation

- 6Appendix

- 7Revision History

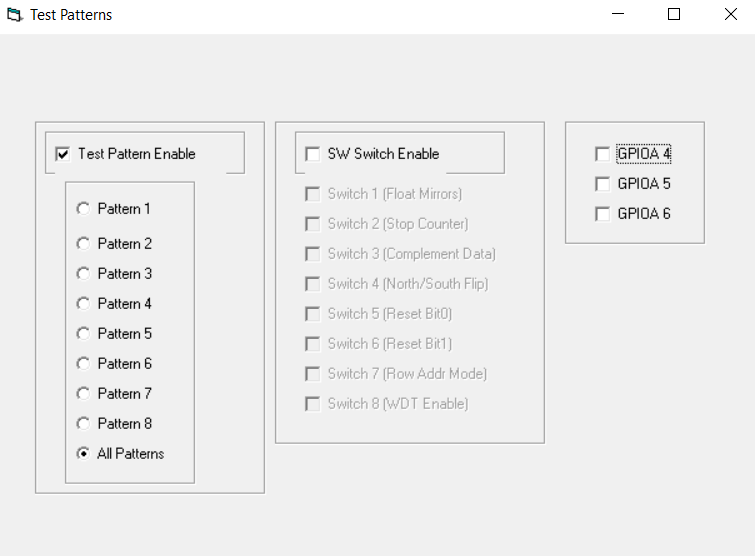

4.6 Test Patterns Window

The Applications FPGA (APPSFPGA) supports two modes.

- Internal Test Patterns Mode - Fixed test patterns stored in the APPSFPGA are selected and displayed on the DMD. This mode does not support scripting.

- User Pattern Mode - User defined images can be downloaded to the APPSFPGA from the GUI for display on the DMD. This is done using the Script Window. When a script is run, the GUI automatically switches to User Pattern Mode even if Internal Test Patterns Mode was previously enabled.

The Test Patterns window is accessed through the Test Patterns menu as seen in #X5612.

Figure 4-30 Test Patterns Window

Figure 4-30 Test Patterns WindowThe Test Patterns window provides the following functions:

- Enable/Disable Internal Test Patterns Mode. If Internal Test Patterns Mode is enabled, then various internal patterns can be selected to display on the DMD. When "All Patterns" is selected then all internal patterns are displayed in round-robin fashion.

- Enable/Disable Software Switch Override. When enabled, this switch overrides the hardware switch settings of switch SW1 found on the DLPLCRC410EVM Controller Board. The HW DIP Switch assignments are repeated here in Table 4-2 for clarity.

- GPIO_A(4 - 6) enable/disable. The [GPIOA 4], [GPIOA 5], and [GPIOA 6] selections in the Test Patterns window map directly to the GPIO_A4, GPIO_A5, and GPIO_A6 outputs of the APPSFPGA, found on connector GPIO_A.

Table 4-2 SW1 Dip Switch Assignments

| HW Switch SW1 Number | Effect |

|---|---|

| 1 | ON = float – float all mirrors |

| 2 | ON = counter halt – stop counter, this freezes the image on the DMD |

| 3 | ON = complement data – causes DLPC410 to complement all data received |

| 4 | ON = north/south flip – causes the DLPC410 to reverse order of row loading, effectively flipping the image |

| 6 and 5 | Dictates the type of reset being used (where switch 6 is the MSB

and ON = 1):

|

| 7 | ON = Row Address Mode |

| 8 | ON = Watchdog Timer (WDT) Enable, disables other resets |

Refer to the DLP Discovery 4100 Development Platform API Programmer’s Guide (DLPU039) for detailed information about the ActiveX functions called by the buttons on this Test Patterns menu page.