SPRACX2 April 2021 TDA4VM , TDA4VM-Q1

- Trademarks

- 1Introduction

- 2What is Structure From Motion?

- 3Introduction to Occupancy Grid Mapping

- 4From Point-Cloud to OG Map

- 5Algorithm Flow: SFM-Based OG Mapping

- 6Algorithm Flow: SFM-Based OG Mapping on TDA4VM

- 7First Example Implementation on TDA4VM

- 8Second Example implementation on TDA4VM

- 9References

6 Algorithm Flow: SFM-Based OG Mapping on TDA4VM

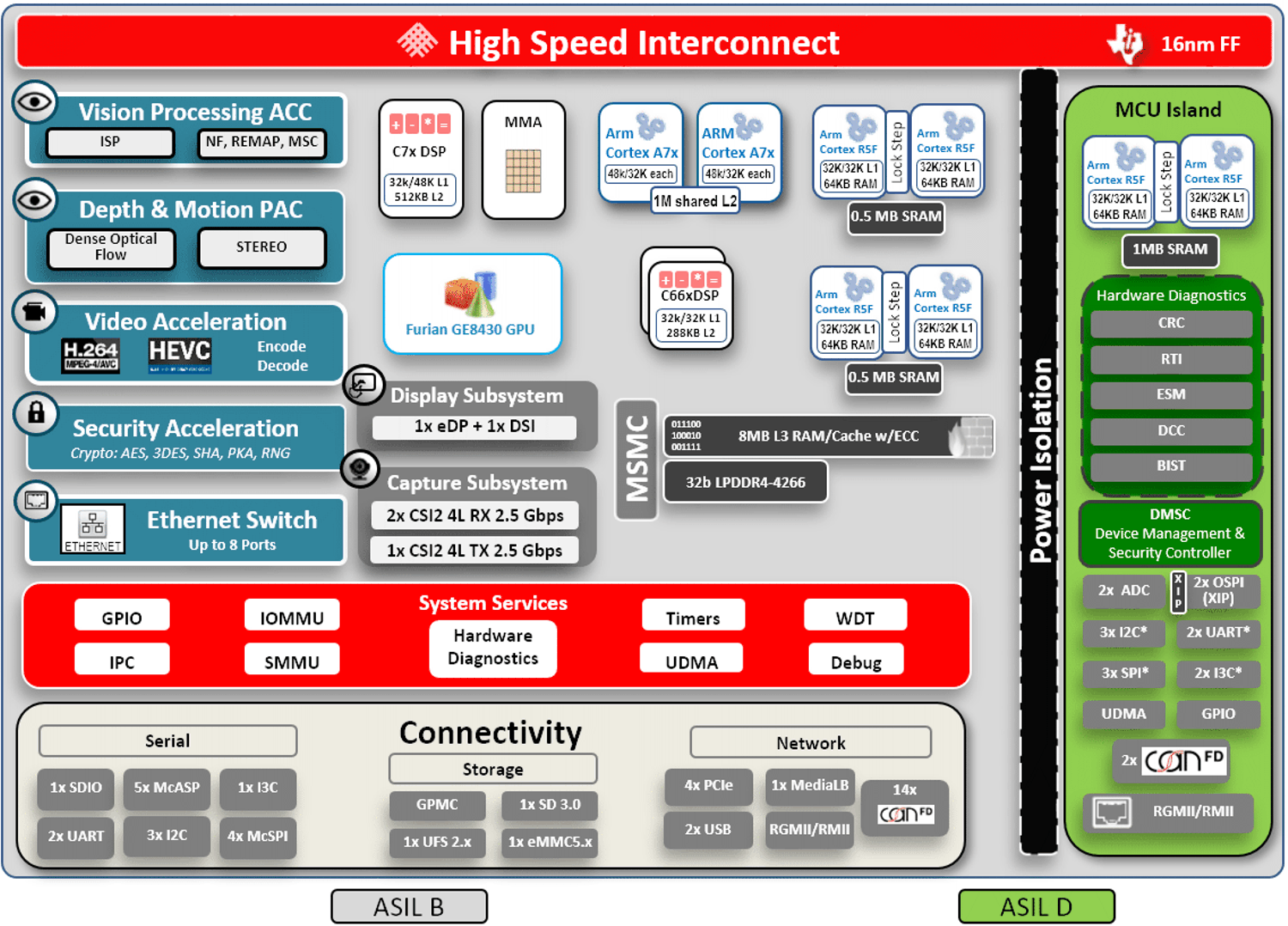

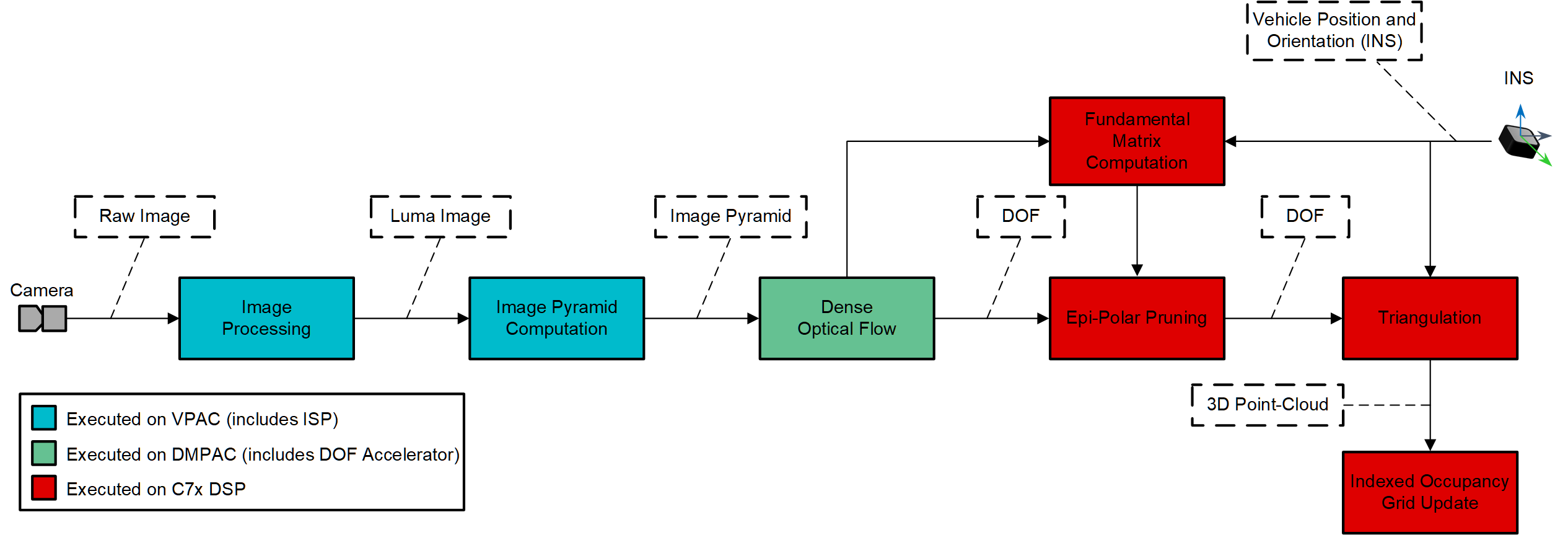

The TDA4VM SoC, which was designed with SFM and other popular Computer Vision tasks necessary for ADAS and robotics in mind, is unsurprisingly uniquely suited for the SFM algorithm. Figure 6-1 shows the TDA4VM device, and Figure 6-2 shows the algorithm flow in Figure 5-1 mapped on to TDA4VM. The Vision Pre-processing Accelerator, or VPAC, mentioned here contains modules to accelerate different image pre-processing sub tasks such as tone mapping, noise filtering, lens distortion correction, and so forth. The Depth and Motion Processing Accelerator, or DMPAC, contains two modules, a Stereo Disparity Engine, or SDE, to accelerate stereo depth estimation, and a Dense Optical Flow Engine, or DOF engine, to accelerate DOF. For more information on the TDA4VM device, see https://www.ti.com/product/TDA4VM.

Figure 6-1 TDA4VM Diagram

Figure 6-1 TDA4VM Diagram Figure 6-2 SFM-Based Occupancy Grid Mapping

Algorithm Flow on TDA4VM

Figure 6-2 SFM-Based Occupancy Grid Mapping

Algorithm Flow on TDA4VMTable 6-1 shows how the sub-tasks of the SFM OG mapping algorithm map are tabulated to the different processors in the TDA4VM SoC.

| Step | TI Processor Silicon IP |

|---|---|

| Raw Image Capture | Imaging Sensor |

| Transmit image to Processor | CSI-2 port |

| Image Processing to form Luma image | Vision Pre-processing Accelerator (VPAC) |

| Image Pyramid Formation | Vision Pre-processing Accelerator (VPAC) |

| Dense Optical Flow Computation | Depth and Motion Processing Accelerator (DMPAC) |

| Epi-Polar Pruning | C7x DSP |

| Fundamental Matrix Computation | C7x DSP |

| Triangulation | C7x DSP |

| Indexed OG map Update | C7x DSP |

Without acceleration through dedicated HWAs, some of these steps are computationally prohibitive. For example, take the DOF portion of the algorithm. For a 2MP camera input, the C7x DSP consumes 2000 Mega Cycles Per Second (MCPS) to generate 2000 key points. Whereas, the DOF HWA only consumes 394 MCPS. Table 6-2 summarizes the results.

| TI Processor Silicon IP | Mega Cycles Per Second (MCPS) |

|---|---|

| DOF HWA on DMPAC | 394 |

| C7x DSP | 2000 |

Furthermore, since all sub-tasks in this algorithm can be performed using the DSPs and HWAs, the general-purpose ARM cores and Deep Learning Accelerators in the TDA4VM device can be reserved for other applications.

Next, two example implementations of SFM OG mapping are described. Both of these applications are included in the SDK that accompanies TDA4x devices. The first, is intended for a vehicle operating on the road, and therefore is designed for input data from a camera mounted in the front of the vehicle. The second, is for automatic parking, and therefore uses input from a camera mounted on the side of the vehicle.