SPRAD53 December 2022 F29H850TU , F29H859TU-Q1 , TMS320F280025C , TMS320F280039C , TMS320F280049C , TMS320F28379D , TMS320F28388D , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4 Software Implementation

This section describes the software implementation used by the C2000 device to identify fail-safes from the AMC1306 device. The project is available within the C2000Ware SDK at [C2000Ware_SDK]\examples\demos\clb_amc_failsafe_monitor. The finite state machine below models the transitions of the states of the delta sigma modulator output depending on the state of the current sensing system. Because the only output signal available externally to the sigma delta modulator is the bitstream itself, a novel software implementation must be used to implement fail-safe monitoring.

For this implementation, the specific devices used are the LAUNCHXL-F280049C and AMC1306EVM. The LAUNCHXL-F280049C is an evaluation module featuring a TMS320F280049C microcontroller clocked at 100 MHz. It has four SDFM modules and four CLB tiles in addition to a variety of on-chip control and communication peripherals. The AMC1306EVM device features an AMC1306M25 device which produces an uncoded (non-Manchester encoded) bitstream and allows for an input voltage range of ±250 mV. In the CLB configuration, it is assumed that the delta-sigma bitstream is uncoded and that the SDFM is operated in Mode 0 clock mode. The same signals which are required inputs to the SDFM peripheral are routed to the CLB peripheral within the device using on-chip interconnects. Being a purely software implementation, this does not require any additional soldering or trace connections.

This software application runs the AMC1306 device at 12.5 MHz, though it can be reconfigured to run at any desired frequency within the delta-sigma modulator's allowed operating frequency range, ranging from 5 MHz up to 20 MHz. The C2000 ePWM1A module generates a 12.5 MHz signal with 50% duty cycle, and this clock signal must be connected to three inputs: the CLKIN input of the AMC1306, the clock input of the SDFM module, and the CLB tile. Per typical current sensing designs, the clock signal generated by the ePWM is externally routed to the delta-sigma modulator and SDFM modules. With the C2000's internal interconnects, the C2000's ePWM signals are directly available to the CLB through a global input bus. Each CLB tile has eight individual inputs, and in this software example, the clock signal is configured as BOUNDARY Input 0 of the CLB tile with a rising-edge detect filter.

The DOUT data bitstream output of the AMC1306 device is fed into the SDFM module's DATA input through a muxed GPIO. The input GPIO signal is available in the input X-BAR, and the CLB has access to this signal through the CLB X-BAR. This DOUT signal is fed into BOUNDARY Input 1 of the CLB. The described DOUT and CLK signal connections are displayed in Figure 4-2.

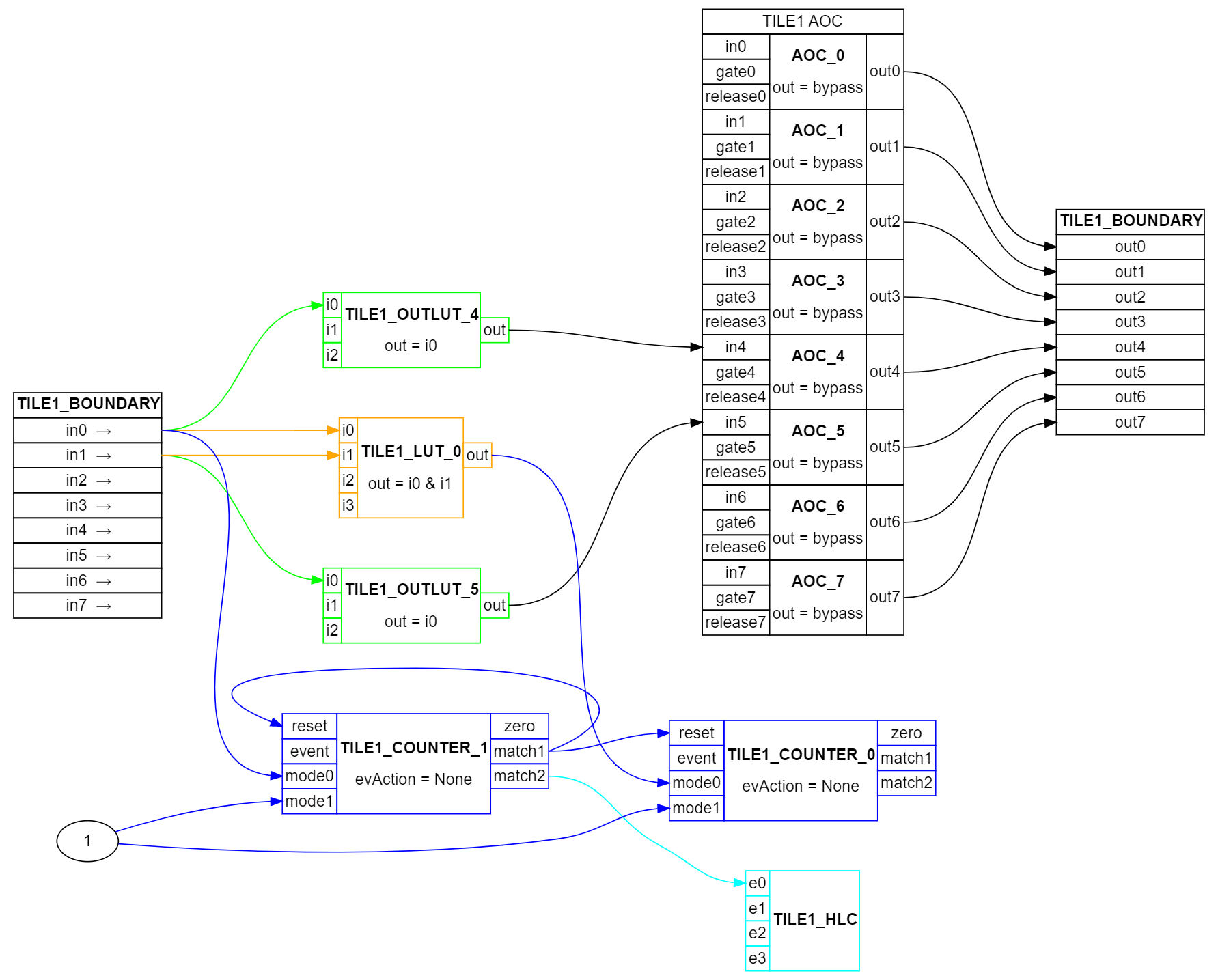

With a combination of the CLK and DOUT signals, the CLB module can read the bitstream at the same frequency as is produced by the delta-modulator. To identify any AMC1306 fail-safe states, the CLB analyzes the DOUT bitstream in 128-bit sections. The 128-bit size is chosen to ensure that full-scale range input states can be differentiated between a missing high-side power or common-mode overvoltage state. The CLB decomposes the bitstream into a ratio of zeros and ones. The implementation within the CLB module is given below:

Figure 4-3 CLB Implementation

Figure 4-3 CLB ImplementationWhen the bitstream consists of constant zero, i.e., the analyzed bitstream segment is 128 0-bits, the CLB understands that the delta-sigma modulator is in a missing high-side fail-safe state. The DSModulatorStatus status indicator variable will then display 2. When the analyzed bitstream segment instead consists of 128 1-bits, it is known that the AMC1306 has a common-mode overvoltage condition.

The negative full-scale range input occurs when the analyzed DOUT pattern consists of 127 0-bits to one 1-bit. A buffer of about 3%, equivalent to three total 1-bits, is given to account for the scenario in which the 1-bit persists for a few additional CLKIN cycles. Similarly, a positive full-scale range input occurs when DOUT is a pattern of 127 1-bits to one 0-bit, with a similar 3% buffer for potential substantially out-of-range inputs.

Table 4-1 provides a summary of delta-sigma modulator statuses and their corresponding DSModulator tag.

| DSModulatorStatus Variable | Delta-Sigma Modulator Status |

|---|---|

| 0 | Transition status |

| 1 | Normal operation |

| 2 | Missing AVDD |

| 3 | Common-mode overvoltage |

| 4 | Negative full-scale range input |

| 5 | Positive full-scale range input |