SPRAD59 October 2023 TMS320F280039

7.2 MCAN Vs DCAN Transmit Procedural Differences

Although the conceptual procedure for transmission is largely identical for DCAN and MCAN, Table 7-1 captures the key differences between both modules:

Table 7-1 MCAN Vs DCAN Transmit Procedure

| Category | DCAN | MCAN |

|---|---|---|

| Transmit Priority | Numerically lowest Message Object (that is ready for transmission) is transmitted first | Buffer containing numerically lowest Message ID (among those ready for transmission) is transmitted first |

| Buffer Type | Only Transmit Message Object | Transmit Buffers can be configured as Dedicated Tx Buffers, Tx FIFO or Tx Queue |

| Writing/Updating Transmit Message | Requires Writes to IFx registers | Transmit Message can be updated by writing directly to Message RAM using Driverlib APIs |

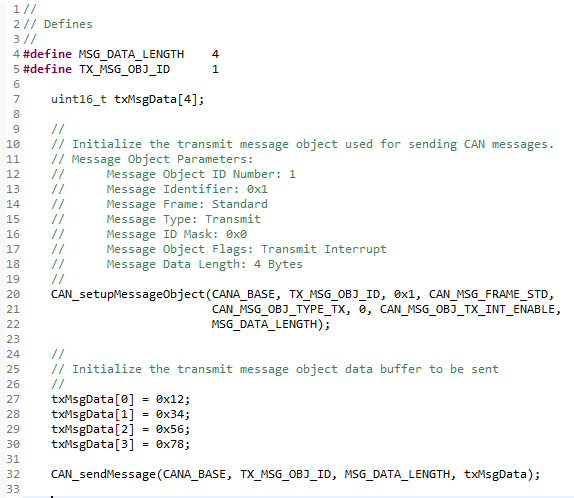

Figure 7-1 Transmission with DCAN

Figure 7-1 Transmission with DCAN