SPRUIR8B april 2020 – july 2023

- 1

- CLB Tool

- Trademarks

- 1Introduction

- 2Getting Started

- 3Using the CLB Tool

-

4Examples

- 4.1

Foundational Examples

- 4.1.1 CLB Empty Project

- 4.1.2 Example 3 – PWM Generation

- 4.1.3 Example 7 – State Machine

- 4.1.4 Example 13 – PUSH-PULL Interface

- 4.1.5 Example 14 – Multi-Tile

- 4.1.6 Example 15 – Tile to Tile Delay

- 4.1.7 Example 16 - Glue Logic

- 4.1.8 Exampe 18 - AOC

- 4.1.9 Example 19 - AOC Release Control

- 4.1.10 Example 20 - CLB XBARs

- 4.2

Getting Started Examples

- 4.2.1 Example 1 – Combinatorial Logic

- 4.2.2 Example 2 – GPIO Input Filter

- 4.2.3 Example 4 – PWM Protection

- 4.2.4 Example 5 – Event Window

- 4.2.5 Example 6 – Signal Generation and Check

- 4.2.6 Example 8 – External AND Gate

- 4.2.7 Example 9 – Timer

- 4.2.8 Example 10 – Timer With Two States

- 4.2.9 Example 11 – Interrupt Tag

- 4.2.10 Example 12 – Output Intersect

- 4.2.11 Example 17 – One-Shot PWM Generation

- 4.2.12 Example 21 - Clock Prescaler and NMI

- 4.2.13 Example 22 - Serializer

- 4.2.14 Example 23 - LFSR

- 4.2.15 Example 24 - Lock Output Mask

- 4.2.16 Example 25 - Input Pipeline Mode

- 4.2.17 Example 26 - Clocking Pipeline Mode

- 4.3 Expert Examples

- 4.1

Foundational Examples

- 5Enabling CLB Tool in Existing DriverLib Projects

- 6Frequently Asked Questions (FAQs)

- 7Revision History

3.2 Updating Variable Paths

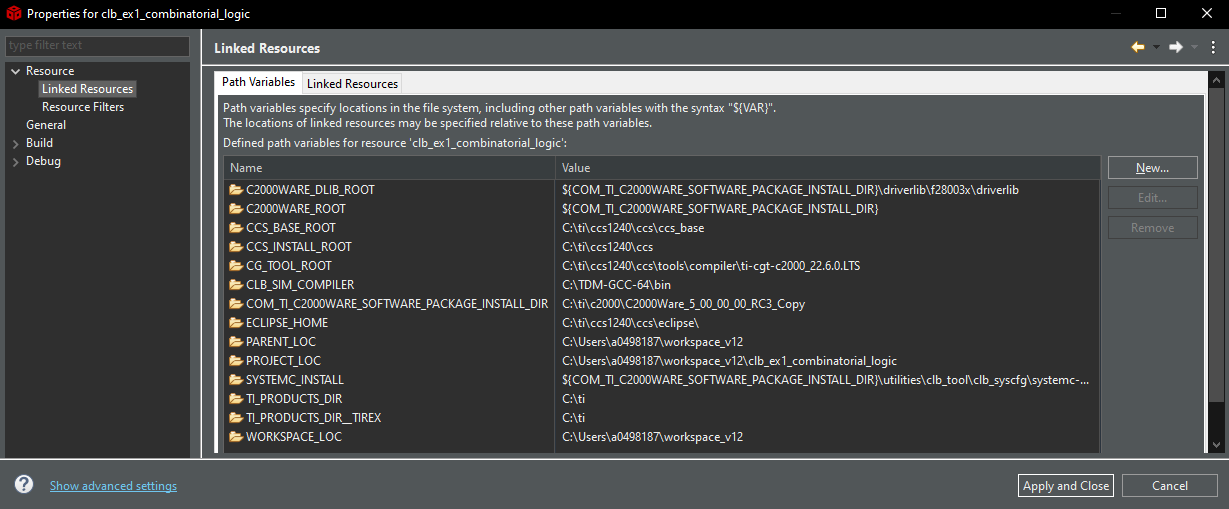

The empty CLB project imported above has the capability to not only generate the “.out” file for the C28x target device, but also has the capability to generate the simulation files and the HTML/SVG block diagram of the design. To create the diagrams using the post-build steps, the proper path must be set for the location of the C2000Ware root and Node tool. To double check that these paths are correct:

- Right click on the project and select ‘Project Properties’.

- Under ‘Resources’, select ‘Linked Resources’.

- Check to make sure the path below is correct:

- C2000WARE_ROOT (This is used for the CLB diagrams and

for other include paths)

Figure 3-2 Linked

Resources

Figure 3-2 Linked

Resources

- C2000WARE_ROOT (This is used for the CLB diagrams and

for other include paths)

- If the icon to the left of the name is not a folder, and is instead an exclamation point, the path does not exist on your system and you must manually select the correct one

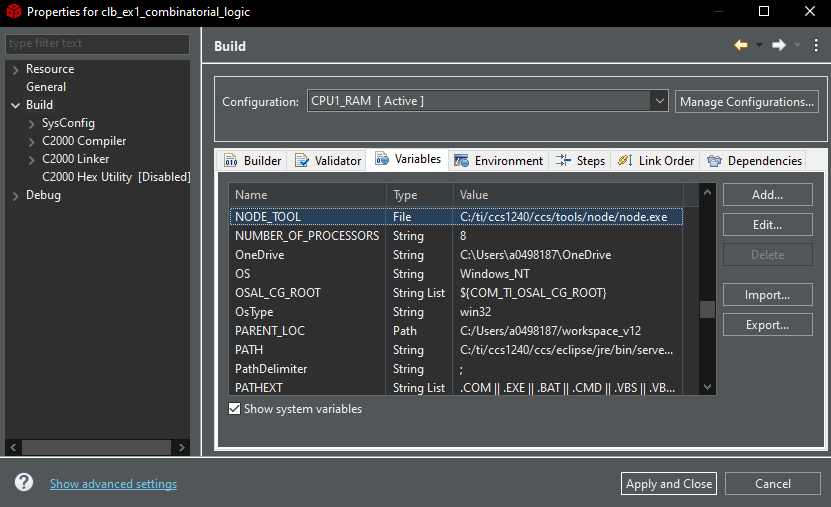

- Check to make sure the path for

the below system variable is correct:

- NODE_TOOL

Figure 3-3 Build

Variables

Figure 3-3 Build

Variables

- NODE_TOOL

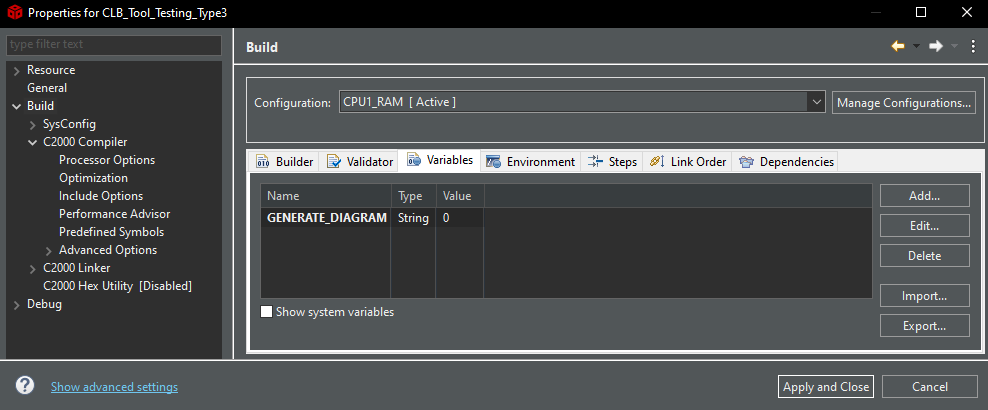

To generate the block diagram, the build variable GENERATE_DIAGRAM must be set to 1. The build variables for a project can be found by going to Project Properties > Build > Variables, as seen in Figure 3-4. This variable enables the post-build steps listed under 'Steps' to run after the project is built. The block diagrams can be found under the relevant build configuration of the project in the 'diagrams' directory, as seen in Figure 5-5.

if ${GENERATE_DIAGRAM} == 1 must be

removed. Figure 3-4 Build Variable to Generate

Diagram

Figure 3-4 Build Variable to Generate

Diagram