SPRUIR8B april 2020 – july 2023

- 1

- CLB Tool

- Trademarks

- 1Introduction

- 2Getting Started

- 3Using the CLB Tool

-

4Examples

- 4.1

Foundational Examples

- 4.1.1 CLB Empty Project

- 4.1.2 Example 3 – PWM Generation

- 4.1.3 Example 7 – State Machine

- 4.1.4 Example 13 – PUSH-PULL Interface

- 4.1.5 Example 14 – Multi-Tile

- 4.1.6 Example 15 – Tile to Tile Delay

- 4.1.7 Example 16 - Glue Logic

- 4.1.8 Exampe 18 - AOC

- 4.1.9 Example 19 - AOC Release Control

- 4.1.10 Example 20 - CLB XBARs

- 4.2

Getting Started Examples

- 4.2.1 Example 1 – Combinatorial Logic

- 4.2.2 Example 2 – GPIO Input Filter

- 4.2.3 Example 4 – PWM Protection

- 4.2.4 Example 5 – Event Window

- 4.2.5 Example 6 – Signal Generation and Check

- 4.2.6 Example 8 – External AND Gate

- 4.2.7 Example 9 – Timer

- 4.2.8 Example 10 – Timer With Two States

- 4.2.9 Example 11 – Interrupt Tag

- 4.2.10 Example 12 – Output Intersect

- 4.2.11 Example 17 – One-Shot PWM Generation

- 4.2.12 Example 21 - Clock Prescaler and NMI

- 4.2.13 Example 22 - Serializer

- 4.2.14 Example 23 - LFSR

- 4.2.15 Example 24 - Lock Output Mask

- 4.2.16 Example 25 - Input Pipeline Mode

- 4.2.17 Example 26 - Clocking Pipeline Mode

- 4.3 Expert Examples

- 4.1

Foundational Examples

- 5Enabling CLB Tool in Existing DriverLib Projects

- 6Frequently Asked Questions (FAQs)

- 7Revision History

6 Frequently Asked Questions (FAQs)

Question: My existing CLB project is not compatible with the latest CLB package. I observe the following build error in CCS problems window: “No such resource: /TILE.syscfg.js”.

Answer: Recent changes in the SysConfig now require the .syscfg file for the project to be modified and updated to reflect the new location of the TILE resource within the CLB package

In order to update the file, you will need to modify the .syscfg file with a text editor.

Update the following line of code:

var TILE = scripting.addModule("/TILE");

replace with

var TILE = scripting.addModule("/utilities/clb_tool/clb_syscfg/source/TILE");

Question: What are the requirements for using the CLB Tool on my computer?

Answer: The minimum requirements are listed below

- C2000Ware 2.00.00.03

- CCSv9.1.0.00010

- Windows 64-bit, Linux, or Mac

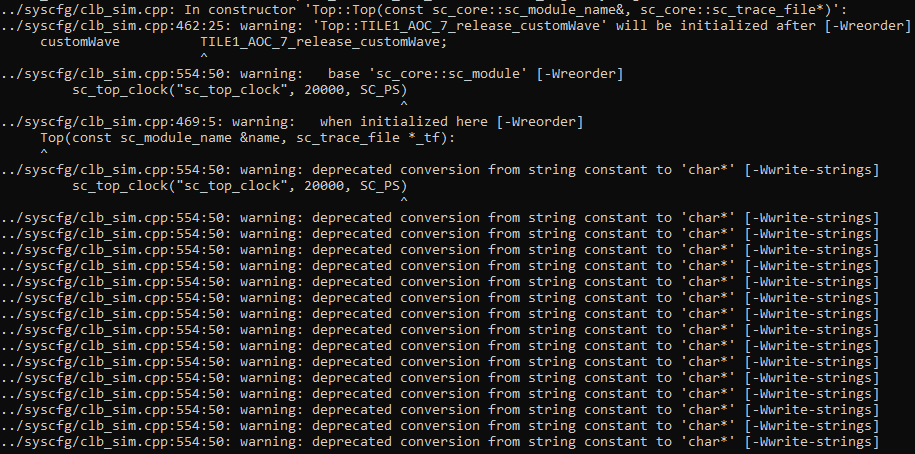

Question: There are many warnings on the console output for generating the .vcd file for CLB simulation, do I need to fix something?

Answer: These warnings can be ignored. They are generated because of the debug message flags which are used in the compile instructions, so they will not affect functionality. Only errors will need to be heeded.

Figure 6-1 Example of Simulation

Warnings

Figure 6-1 Example of Simulation

Warnings