DLPS029F April 2013 – May 2019 DLPC350

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 I/O Electrical Characteristics

- 6.6 I2C0 and I2C1 Interface Timing Requirements

- 6.7 Port 1 Input Pixel Interface Timing Requirements

- 6.8 Port 2 Input Pixel Interface (FPD-Link Compatible LVDS Input) Timing Requirements

- 6.9 System Oscillator Timing Requirements

- 6.10 Reset Timing Requirements

- 6.11 Video Timing Input Blanking Specification

- 6.12 Programmable Output Clocks Switching Characteristics

- 6.13 DMD Interface Switching Characteristics

- 6.14 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZFF|419

Thermal pad, mechanical data (Package|Pins)

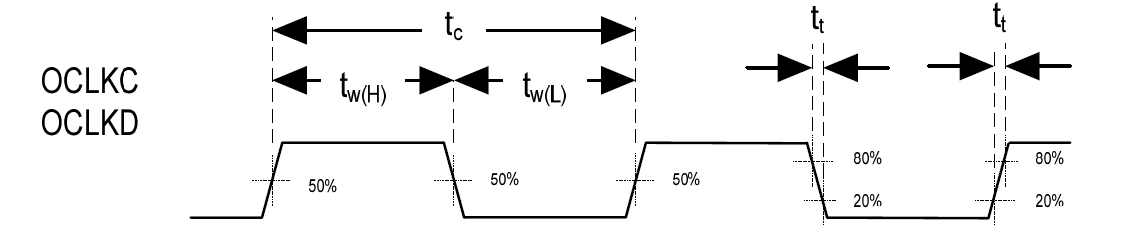

6.12 Programmable Output Clocks Switching Characteristics

| PARAMETER | FROM (INPUT) | TO (OUTPUT) | MIN | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ƒclock | Clock frequency, OCLKC(1) | N/A | OCLKC | 0.7759 | 48 | MHz |

| tc | Cycle time, OCLKC(2) | N/A | OCLKC | 20.83 | 1288.80 | ns |

| tw(L) | Pulse duration low (50% reference points) | N/A | OCLKC | (tc / 2) – 2 | ns | |

| tw(H) | Pulse duration high (50% reference points) | N/A | OCLKC | (tc / 2) – 2 | ns | |

| ƒclock | Clock frequency, OCLKD(1) | N/A | OCLKD | 0.7759 | 48 | MHz |

| tc | Cycle time, OCLKD(2) | N/A | OCLKD | 20.83 | 1288.80 | ns |

| tw(L) | Pulse duration low (50% reference points) | N/A | OCLKD | (tc / 2) – 2 | ns | |

| tw(H) | Pulse duration high (50% reference points) | N/A | OCLKD | (tc / 2) – 2 | ns | |

(1) The frequency of OCLKC and OCLKD is programmable. See GPIO pins 11 and 12.

(2) The duty cycle of OCLKC and OCLKD will be within ±2 ns of 50%.

Figure 8. Programmable Output Clocks Timing Diagram

Figure 8. Programmable Output Clocks Timing Diagram