JAJSPX7E February 2023 – April 2024 TLV709

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 詳細説明

- 7 アプリケーションと実装

- 8 デバイスおよびドキュメントのサポート

- 9 改訂履歴

- 10メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- PK|3

発注情報

6.3.3 ドロップアウト電圧 (VDO)

ドロップアウト電圧 (VDO) は、パス トランジスタが完全にオンになる定格出力電流 (IRATED) において、VIN - VOUT として定義されます。VIN は入力電圧、VOUTは出力電圧、IRATED は 推奨動作条件 表に記載されている最大 IOUT です。ドロップアウト動作では、パス トランジスタはオーム領域または三極管領域で動作し、スイッチとして機能します。ドロップアウト電圧は、出力電圧がレギュレーション状態を維持すると予想される、プログラムされた公称出力電圧よりも大きな最小入力電圧を間接的に規定します。入力電圧が出力レギュレーションを維持するために必要な値よりも低下すると、出力電圧も同様に低下します。

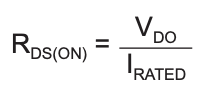

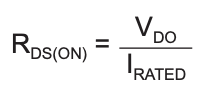

CMOS レギュレータの場合、ドロップアウト電圧はパス トランジスタのドレイン ソース間オン抵抗 (RDS(ON)) によって決まります。したがって、リニア レギュレータが定格電流よりも低い値で動作する場合、その電流に対するドロップアウト電圧はそれに応じてスケーリングされます。式 1 を使用して、デバイスの RDS(ON) を計算します。

式 1.