JAJU446A December 2017 – January 2022

- 概要

- Resources

- 特長

- アプリケーション

- 5

- 1 System Description

- 2 System Overview

- 3 Circuit Design

- 4 Host Interface

- 5 Hardware Functional Block

- 6 Getting Started Application GUI

- 7 Testing and Results

- 8 Design Files

- 9 Software Files

- 10Related Documentation

- 11About the Authors

- 12Revision History

5 Hardware Functional Block

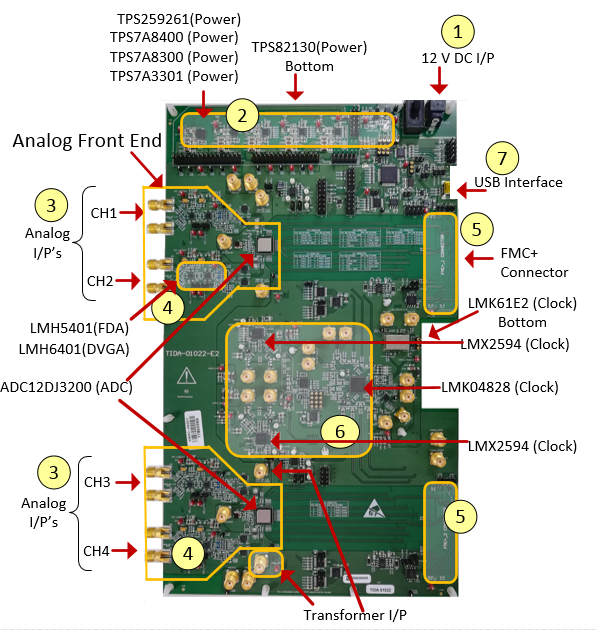

Figure 5-1 shows the various hardware functional blocks of the TIDA-01022 design and the function of each block:

- A 12-V DC power supply input connector accepts the 9- to 12-V DC input to power the TIDA-01022

- Power supply section has switching regulator (DC-DC) and LDOs to generate multiple rails (1.1 V,

1.9 V, 3.3 V, +2.5 V, and –2.5 V) from the 12-V input - Four analog input channels which the designer can configure to accept 50-Ω single-ended or differential inputs

- AFE block contains combination of LMH5401+LMH6401, which accepts both AC and DC coupled inputs up to 1.5 GHz; optional transformer-coupled inputs are also available for an AC-coupled application up to 6 GHz

- FMC+ connector interfaces with TI High-Speed Data Capture card to the TSW14J56 using an FMC+ to FMC adapter PCB

- Clock subblock which contains high-performance clocking solution native to LMK04828, LMK2594, LMK00304, and LMK61E2 clocking devices

- Mini-USB interface connector helps to configure ADCs and clocking devices for various modes

Figure 5-1 TIDA-01022 Hardware Functional Block

Figure 5-1 TIDA-01022 Hardware Functional Block