SLUP409B April 2022 – April 2024 TPS543320 , TPS543620 , TPS543820 , TPS62913 , TPS62916

- 1

- Abstract

- 1 Introduction

- 2 DC/DC Converters are Noisy

- 3 Power-Supply Output Voltage Ripple and Noise Degrade ADC Performance

- 4 Minimizing Low-Frequency Noise Requires Dedicated Low-Noise IC Technologies

- 5 Traditional Approaches to Reducing Ripple

- 6 Using Smaller Capacitors in Parallel

- 7 Larger Inductance

- 8 Adding a Feedthrough Capacitor

- 9 Adding a Ferrite Bead

- 10Layout Techniques

- 11Silicon Solutions

- 12Conclusions

2 DC/DC Converters are Noisy

DC/DC switching converters are well known for high efficiency and a relatively small solution size. They are also well known for their larger output voltage ripple and high-frequency noise, which is caused by DC/DC converter switching cycles.

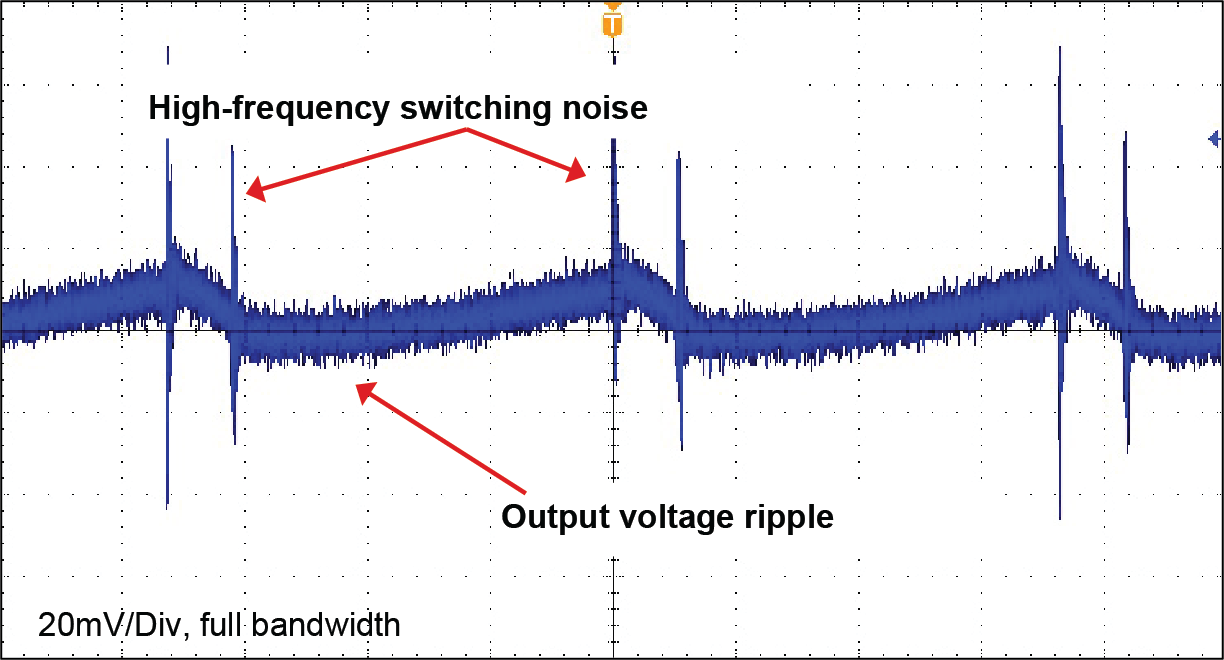

Figure 1 shows an example of the output voltage for a standard DC/DC buck converter. The output voltage ripple shows high-frequency switching noise, output capacitor voltage ripple and general low-frequency noise. Applying this waveform to a noise-sensitive system will reduce signal quality.

Looking at high-speed ADCs, the spurious-free dynamic range (SFDR) and signal-to-noise ratio (SNR) are reduced when using a typical DC/DC buck converter, as shown in Figure 3. Frequency synthesizers and phase-locked loops (PLLs) show degradation in phase noise, having larger jitter when powered by a supply rail, as seen in Figure 3.

Figure 1 Typical output voltage ripple

of a DC/DC buck converter.

Figure 1 Typical output voltage ripple

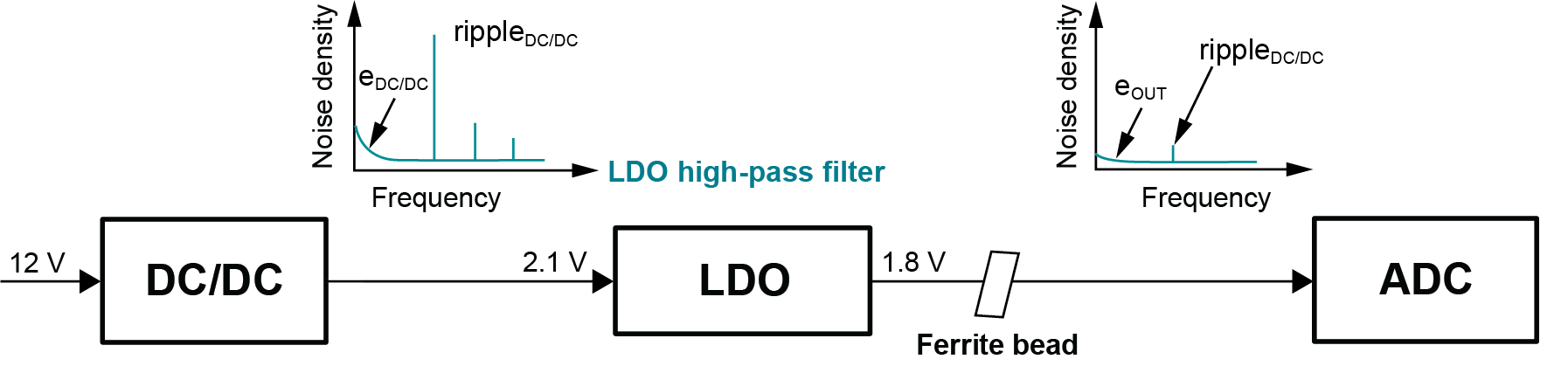

of a DC/DC buck converter.There are several ways to minimize power-supply output ripple and low- and high-frequency noise. Figure 2 shows the traditional approach, using an LDO as a post-filter and a ferrite bead as a high-frequency filter.

Figure 2 Traditional LDO post-filtering

is large in size, with high power loss at load currents >2A.

Figure 2 Traditional LDO post-filtering

is large in size, with high power loss at load currents >2A.The LDO is simple to use and a popular approach for moderate load currents. For load currents beyond 2A, however, the power loss in the LDO increases to 600mW or more. Compensating for this power loss requires the selection of larger LDO packages, making the solution more expensive and generating excessive system heat – a problem for 5G telecom systems that require several analog front ends (AFEs).

In test and measurement applications, high-speed ADCs require power-supply load currents ≥2A. In order to reduce the power dissipation and solution size for these types of applications, it is advantageous to power the rails directly from the DC/DC converter without LDO post-filtering, but then the DC/DC converter needs to achieve a similar output voltage quality in terms of noise and ripple compared to the LDO.

The LDO filters the output voltage ripple of the DC/DC converter at the converter switching frequency (fSW), which is typically in a range from 100kHz to 2MHz. The power-supply rejection ratio (PSRR) expresses the effectiveness of the LDO to filter noise – it is the attenuation of the input voltage ripple and noise. Most LDOs are optimized for low noise at a frequency range below 100kHz and will not filter high-frequency components, therefore necessitating a ferrite bead and bypass capacitor after the LDO for additional high-frequency filtering. With these considerations, it becomes possible to derive a target specification for a DC/DC converter to power noise-sensitive systems. For example, a system with a high-speed ADC may require noise levels below 20µVRMS, a maximum output voltage ripple of 200µVpp and a PSRR >30 dB at frequencies of 1 MHz and beyond.