SLVUBT8B November 2020 – June 2022 LP8764-Q1 , TPS6594-Q1

- Scalable PMIC's GUI User’s Guide

- Trademarks

- 1 Introduction

- 2 Supported Features

- 3 Revisions

- 4 Overview

- 5 Getting Started

- 6 Quick-start Page

- 7 Register Map Page

- 8 NVM Configuration Page

- 9 NVM Validation Page

- 10Watchdog Page

- 11Additional Resources

- 12Appendix A: Troubleshooting

- 13Appendix B: Advanced Topics

- 14Appendix C: Known Limitations

- 15Appendix D: Migration Topics

- 16Revision History

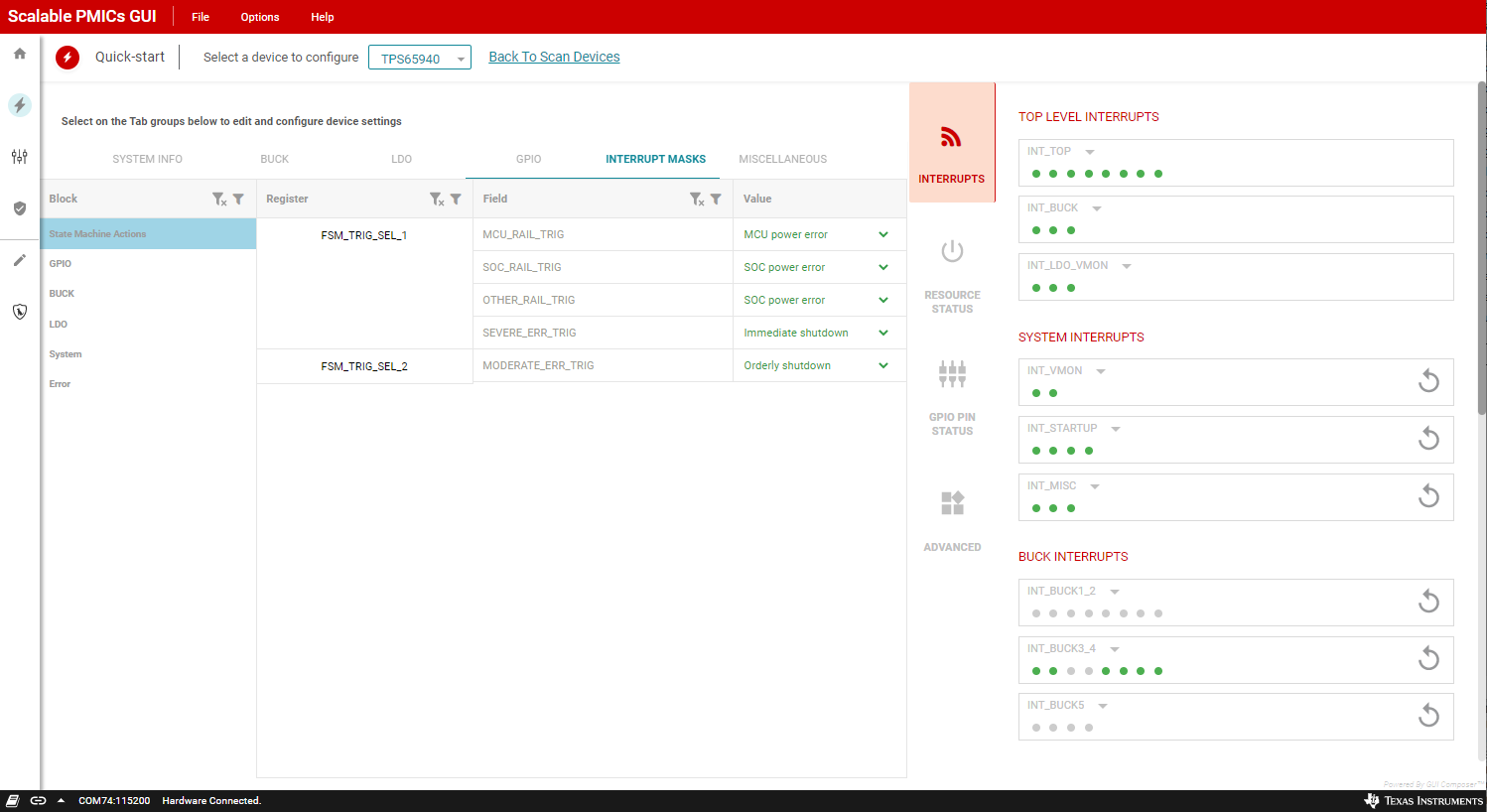

6.2.5 Interrupts

From the interrupts tab the user can decide to mask or monitor various interrupt sources: State Machine, GPIOs, BUCKs, and so on.

The interrupt status, shown on the right side of Figure 6-8, can be used to monitor the interrupt events. The interrupts are grouped according to function and can be expanded to see each individual interrupt source. TOP LEVEL INTERRUPTS are read only and cannot be cleared. Other interrupts can be cleared at a register or bit level, as indicated by the reset symbol. An ERROR status with a red dot indicates that an interrupt has occurred while a NORMAL status with a green dot indicates that no interrupt has occurred or that the interrupt has been cleared. Typically, gray represents interrupts which are masked. If an interrupt has a NORMAL status with a gray dot, then this indicates that the interrupt is not applicable for the specified phase configuration. The GUI will ignore any attempt to unmask or generate an interrupt that is not applicable to the device phase configuration.

Figure 6-8 Interrupt Mask and Status

Figure 6-8 Interrupt Mask and Status