SPRACW5A April 2021 – December 2021 F29H850TU , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Trademarks

- 1Introduction

- 2ACI Motor Control Benchmark Application

- 3Real-time Benchmark Data Analysis

-

4C2000 Value Proposition

- 4.1 Efficient Signal Chain Execution With Better Real-Time Response Than Higher Computational MIPS Devices

- 4.2 Excellent Real-Time Interrupt Response With Low Latency

- 4.3 Tight Peripheral Integration That Scales Applications With Large Number of Peripheral Accesses

- 4.4 Best in Class Trigonometric Math Engine

- 4.5 Versatile Performance Boosting Compute Engine (CLA)

- 4.6 Deterministic Execution due to Low Execution Variance

- 5Summary

- 6References

- 7Revision History

3.1 ADC Interrupt Response Latency

Interrupt latency is an important factor in understanding the response time of a real-time system. The typical method by which interrupt latency of a system is assessed is the number of cycles it takes for the hardware to respond to an interrupt and branch to the interrupt vector (hardware latch and respond). However, in a real-time application this is only part of the response latency.

Consider the sensorless ACI motor benchmark application, the PWM triggers the ADC to initiate sampling. The ADC takes a certain number of cycles to finish sampling or conversion, which is dependent on the system configuration as well as ADC capability. Once the ADC is ready it generates an interrupt. In the ACI motor benchmark the ADC is configured for early interrupt generation where the interrupt is generated after sampling completes and just as conversion starts instead of at the end of conversion. Once the ADC generates the interrupt, the hardware responds to the interrupt and branches to the interrupt vector. However, the interrupt service routine does not start executing user code right away but before that can happen some compiler generated context save must be performed and then the user code is executed.

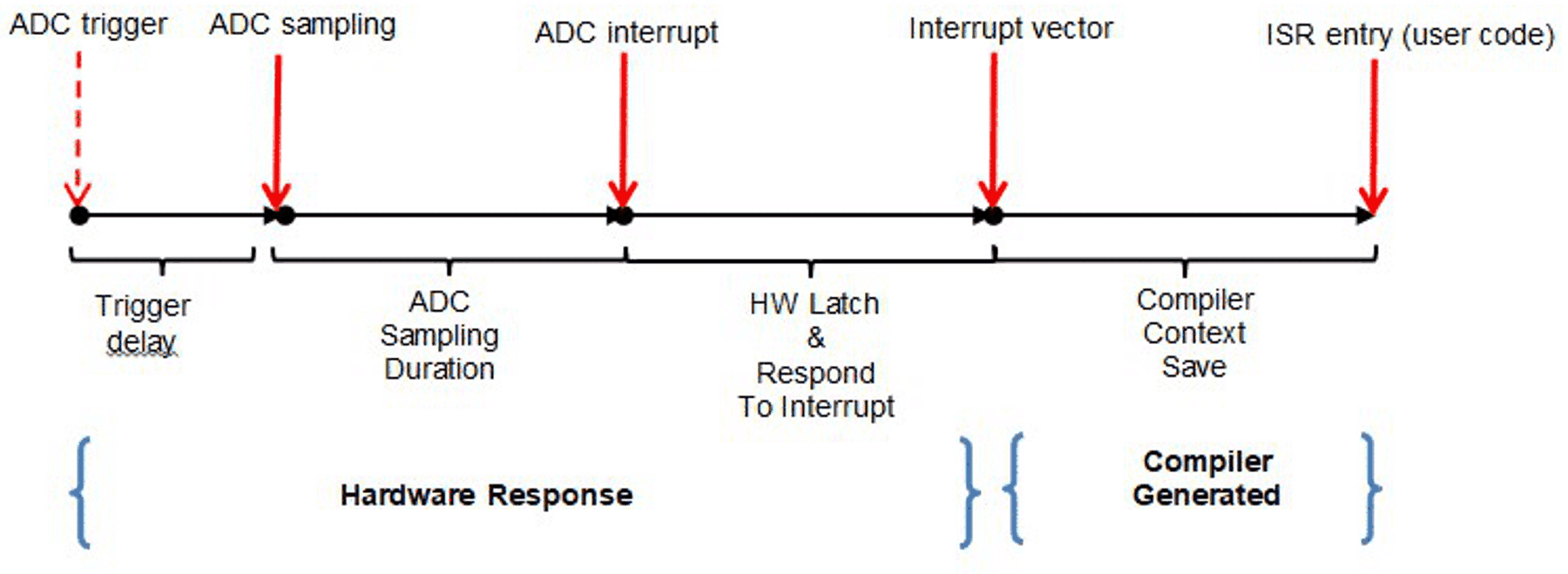

In effect, as illustrated in the Figure 3-1, the real interrupt latency is an aggregate of four components: trigger delay + ADC sampling duration + hardware latch and respond + compiler generated context save.

Figure 3-1 ACI Motor Benchmark Interrupt

Response Components

Figure 3-1 ACI Motor Benchmark Interrupt

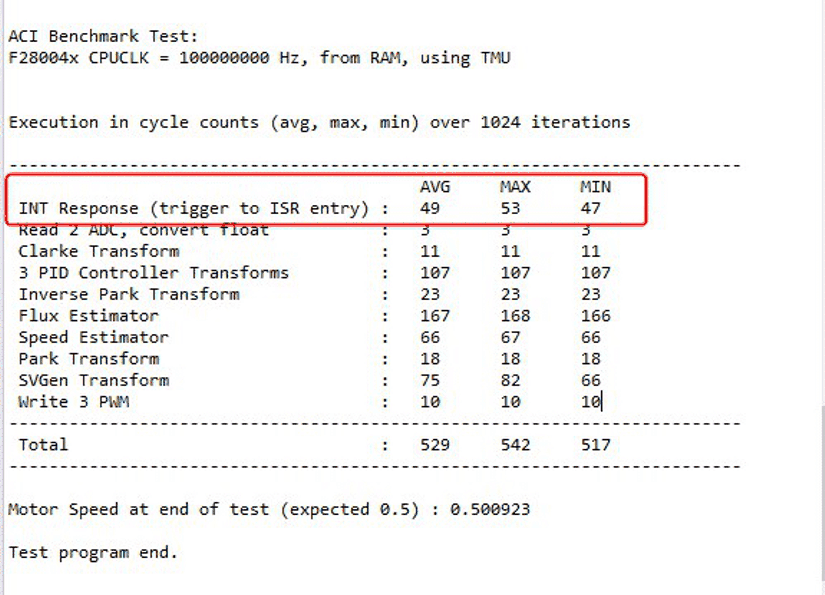

Response ComponentsThe ACI real-time benchmark outputs this value as "INT Response (trigger to ISR entry)". As can be seen in Figure 3-2, the C28x INT response time on an average is 49 cycles and represents the real latency for when an application can start responding to a sensing event for the sensorless ACI motor example. Traditional benchmarks do not measure the system in this fashion. The variance in the INT response cycles between the Min and Max value is expected as there may be additional cycles needed to complete an ongoing background instruction before the asynchronous interrupt event can be taken by the CPU.

Figure 3-2 ACI Motor Benchmark Interrupt

Response Benchmark Data

Figure 3-2 ACI Motor Benchmark Interrupt

Response Benchmark DataTable 3-1 lists a theoretical estimate of the contribution of each individual element and as can be seen the total cycles aligns with the minimum cycles benchmarked by the application.

| Trigger Delay (1) | ADC Sampling Duration (2) | HW Latch and Response(3) | Compiler Context Save(4) | Total (cycles) |

|---|---|---|---|---|

| 2 | 8 | 14 | 23 | 47 |

A look at the individual components that contribute to the total cycles shows that the PWM and ADC are closely integrated and the trigger delay contributes to few additional cycles. The ADC early interrupt generation feature allows the ADC conversion to proceed in parallel while the system is responding to the interrupt. This allows the conversion cycles to overlap with the interrupt generation and compiler context save cycles, thus reducing the overall time required for responding to the ADC sampling event. In comparison, for any other system that does not have the ADC early interrupt generation feature, the interrupt response will include the conversion cycles thus increasing the overall response time. The other advantage of this feature is that ADC result can be applied to the system closer in time to when it was sampled resulting in more accurate system control.