SPRACY1 May 2021 F29H850TU , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P550SG , TMS320F28P550SJ , TMS320F28P559SG-Q1 , TMS320F28P559SJ-Q1 , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.1 Shadow to Active Load on SYNC

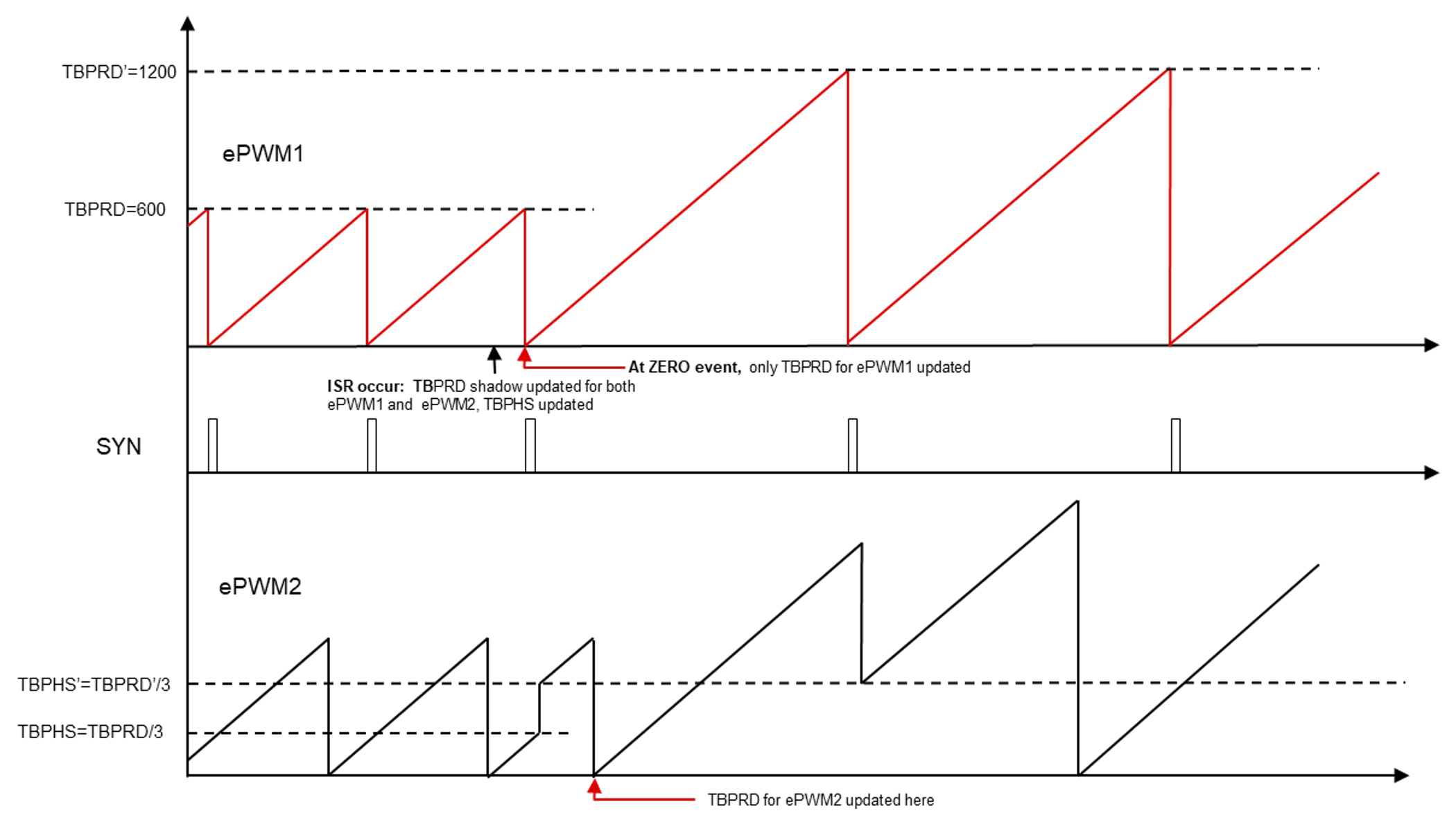

In the previous generation C2000 devices, with Type 0 or Type 1 ePWM, the shadow register contents are transferred to the active register (TBPRD (Active) ← TBPRD (shadow)) when the time-base counter equals zero (TBCTR = 0x0000). It might cause the phase mismatch issue during variable frequency applications.

Figure 2-2 shows one example with 2 phase interleaved control, using 120° phase shift between ePWM1 and ePWM2 modules. And the ePWM1_ZERO event is selected as the SyncIn pulse for ePWM2. Assuming the ISR, to change the frequency, occurs between the ePWM1_ZERO event and ePWM2_ZERO event, and the TBPRD shadow registers of both ePWM1 and ePWM2 are updated with the new period value (1200), and TBPHS of ePWM2 is updated with 400 immediately. As shown in the waveforms, since the active TBPRD value can not be updated until the next ePWM2_ZERO event, so the phase shift relation is incorrect right after the frequency changes. Even worse, if the new TBPHS value of ePWM2 is larger than the previous period register value, it might cause unpredictable results when the TBCTR is loaded with this value at SyncIn event. As a result, the time-base counter keeps counting up beyond the period register value and goes all the way until it eventually rolls over.

Figure 2-2 Phase Control Limitation With the

Previous Generation C2000 Devices

Figure 2-2 Phase Control Limitation With the

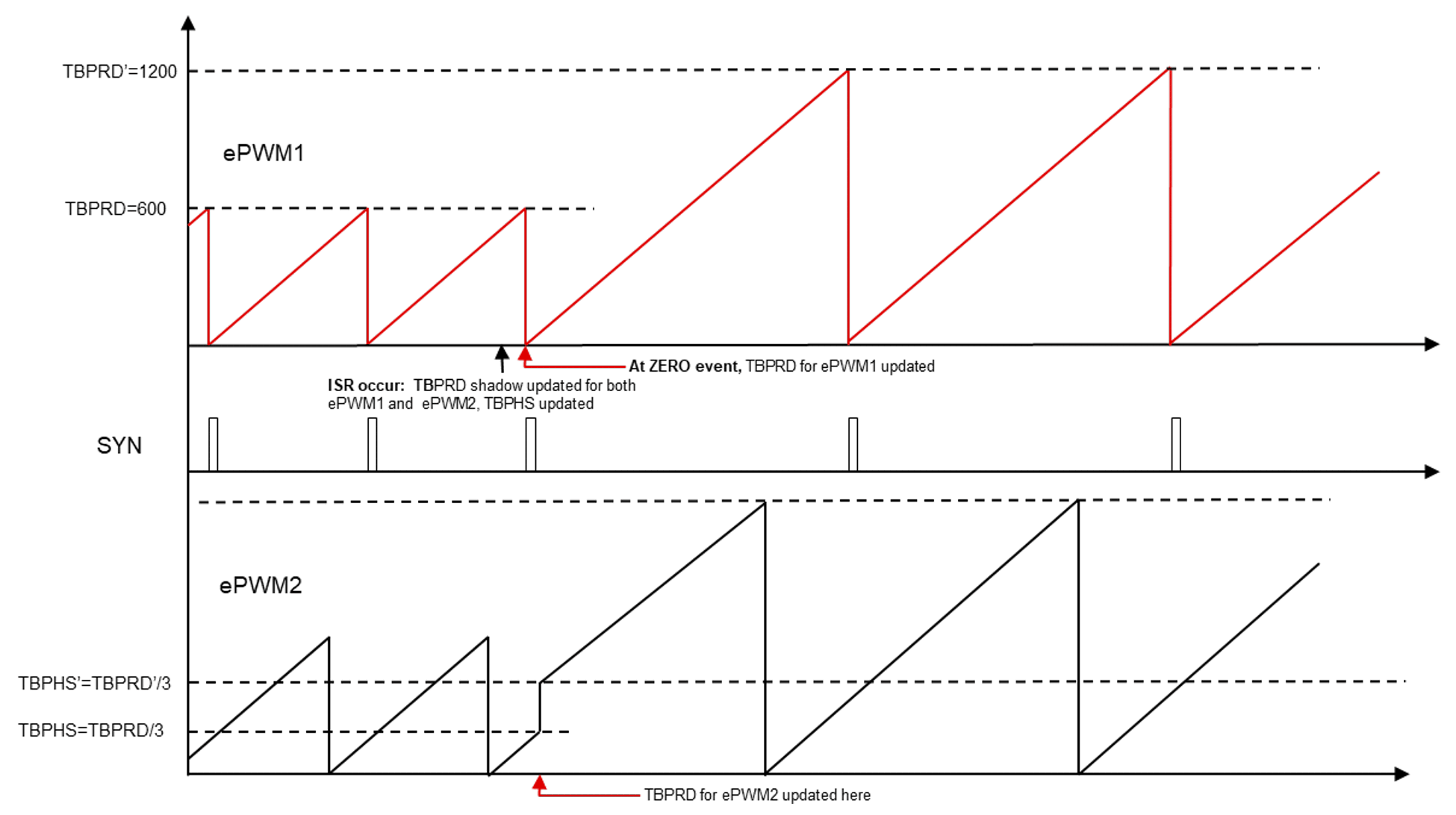

Previous Generation C2000 DevicesThe above risk has been resolved from Type 2 ePWM, which enables a sync event additionally, as determined by the TBCTL2[PRDLDSYNC] bit, to make the shadow to action loading effective for TBPRD and CMP registers. In this way, the correct phase shift can be obtained as shown in Figure 2-3.

Figure 2-3 Correct Phase Shift Control With

Shadow to Active Load at Sync Event

Figure 2-3 Correct Phase Shift Control With

Shadow to Active Load at Sync Event