TIDUD61E October 2020 – April 2021

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1

Required Hardware and Software

- 3.1.1 Hardware

- 3.1.2

Software

- 3.1.2.1 Opening Project Inside CCS

- 3.1.2.2 Project Structure

- 3.1.2.3 Using CLA on C2000 MCU to Alleviate CPU Burden

- 3.1.2.4 CPU and CLA Utilization and Memory Allocation

- 3.1.2.5

Running the Project

- 3.1.2.5.1 Lab 1: Open Loop, DC (PFC Mode)

- 3.1.2.5.2 Lab 2: Closed Current Loop DC (PFC)

- 3.1.2.5.3 Lab 3: Closed Current Loop, AC (PFC)

- 3.1.2.5.4 Lab 4: Closed Voltage and Current Loop (PFC)

- 3.1.2.5.5 Lab 5: Open loop, DC (Inverter)

- 3.1.2.5.6 Lab 6: Open loop, AC (Inverter)

- 3.1.2.5.7 Lab 7: Closed Current Loop, DC (Inverter with resistive load)

- 3.1.2.5.8 Lab 8: Closed Current Loop, AC (Inverter with resistive load)

- 3.1.2.5.9 Lab 9: Closed Current Loop (Grid Connected Inverter)

- 3.1.2.6 Running Code on CLA

- 3.1.2.7

Advanced Options

- 3.1.2.7.1 Input Cap Compensation for PF Improvement Under Light Load

- 3.1.2.7.2 83

- 3.1.2.7.3 Adaptive Dead Time for Efficiency Improvements

- 3.1.2.7.4 Phase Shedding for Efficiency Improvements

- 3.1.2.7.5 Non-Linear Voltage Loop for Transient Reduction

- 3.1.2.7.6 Software Phase Locked Loop Methods: SOGI - FLL

- 3.2 Testing and Results

- 3.1

Required Hardware and Software

- 4Design Files

- 5Software Files

- 6Related Documentation

- 7About the Author

- 8Revision History

3.1.2.5.5.4 Running Code

- Now run the project again by clicking on

.

. - In a few seconds the inrush relay clicks, the software is programmed to do so in the lab with DC. The trip clears, and a duty cycle of 0.5 is applied.

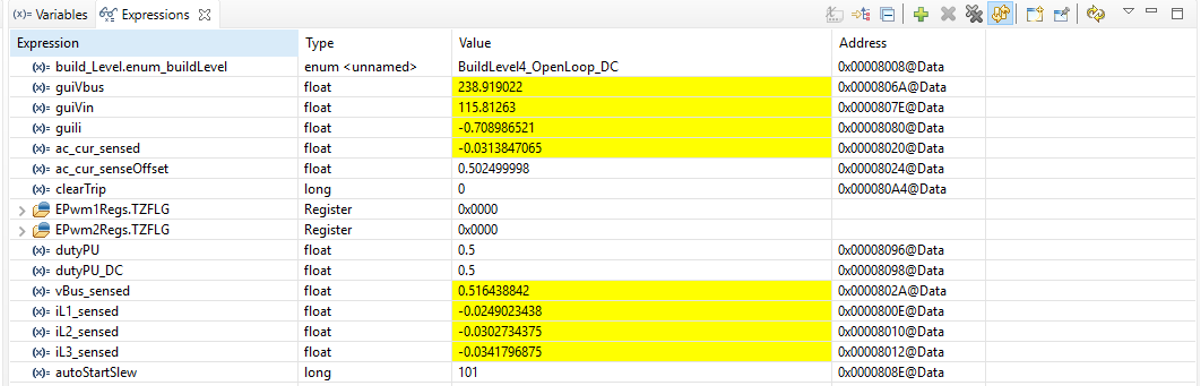

- In the watch view, check if the guiVin, guiVbus, guiIi, variables are updating, periodically.

- Note: As no power is applied right now, this value is close to zero.

- Now slowly increase the input DC voltage from zero to 240 V. The output voltage shows a step down voltage (buck converter operation) as a steady duty cycle of 0.5 PU is applied as default setting. If a high current is drawn, verify if the voltage terminals are swapped. If true, reduce the voltage to zero first and correct the issue before resuming the test

- Verifying the voltage sensing: Make sure TTPLPFC_ac_vol_sensed_Volts and TTPLPFC_vBus_sensed_Volts display the correct values, for 240-V DC input, TTPLPFC_ac_vol_sensed_Volts is close to 120V. This verifies the voltage sensing of the board in some manner.

- Verifying the current sensing: Notice the TTPLPFC_ac_curRms_sensed_Amps for the given test condition; this value is close to 1 A.

Figure 3-32 Lab 5 Watch Expression Showing Measured Voltage and Currents

Figure 3-32 Lab 5 Watch Expression Showing Measured Voltage and Currents - Once finished, reduce the input voltage to zero and watch for the bus voltages to reduce down to zero.

- This completes the check for this build, the following items are verified on successful completion of this build:

- Sensing of voltages and currents and scaling to be correct

- Interrupt generation and execution of the LAb 5 code in the current loop ISR and Voltage Loop Instrumentation ISR

- PWM driver and switching

- The controller can now be halted, and the debug connection terminated.

- Fully halting the MCU when in real-time mode is a two-step process. First halt the processor by using the Halt button on the toolbar (

) or by using Target → Halt. Then take the MCU out of real-time mode by clicking on

) or by using Target → Halt. Then take the MCU out of real-time mode by clicking on  . Finally, reset the MCU by clicking on

. Finally, reset the MCU by clicking on  .

. - Close CCS debug session by clicking on Terminate Debug Session (Target → Terminate all).