DLPU113A December 2021 – April 2022 DLP2021-Q1

4.3 MSP430 Example Code

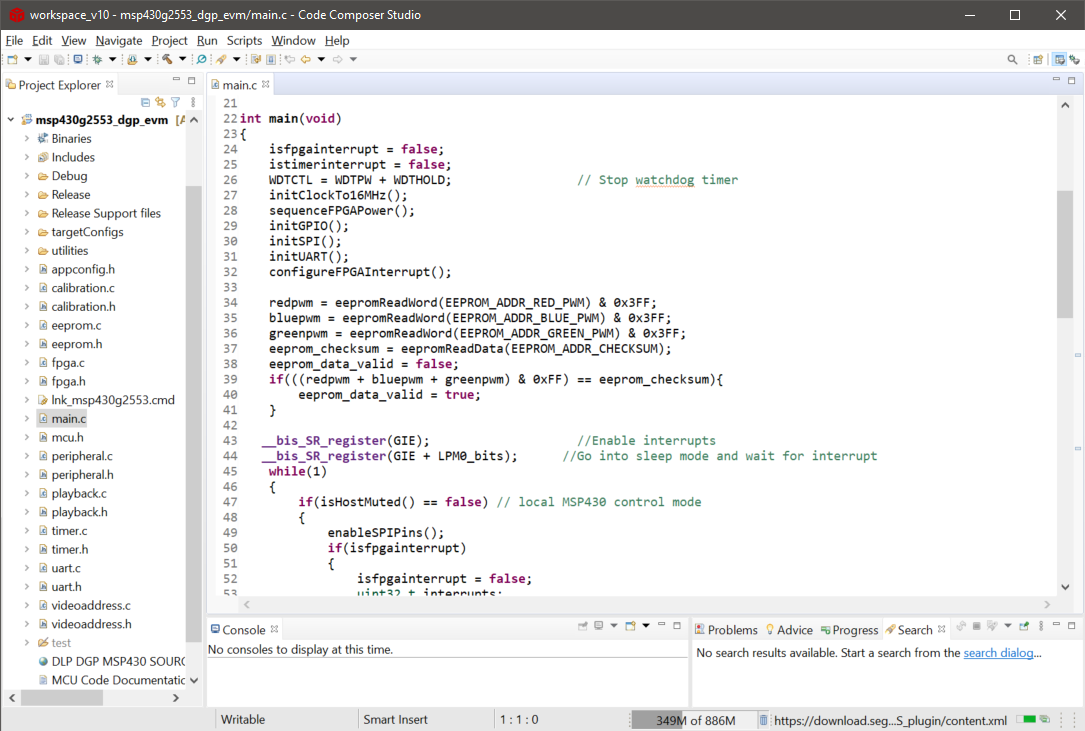

When power is applied to the system, the FPGA configuration is loaded to the FPGA. Depending on the default configuration, the FPGA begins loading bit-planes to the DMD and sequencing the LED enables for each bit plane loaded. Alternatively, a microcontroller such as the MSP430G2553-Q1 on the EVM, can issue commands to the FPGA via SPI to enable video playback, change videos, read DMD temperature via the TMP411, or adjust current levels to the LEDs. The MSP430 Example Code (DLPC138) is a Code Composer Studio example project available for users to edit and refer to for a custom Local Host Control operation mode implementation.

Figure 4-15 MSP430G2553-Q1 Code Composer Example Project for DGP EVM

Figure 4-15 MSP430G2553-Q1 Code Composer Example Project for DGP EVM