SNAU266A July 2021 – August 2022

3.2 SYSREF Generation

The SYSREF generation circuit includes a SYSREF pre-divider and post-divider, a pulser with programmable pulse quantity, and a repeater mode bypass. The SYSREF generator modes re-time the SYSREF signal to the output clock, ensuring the SYSREF output is close to the falling edge of the clock output with default delay settings. Repeater mode timing is solely determined by the propagation delay of the device.

To activate the SYSREF generation circuit, the following conditions must be satisfied:

- SRREQ_MODE field must be set to SYSREFREQ mode

- SYSREF_MODE field must be set to the appropriate condition: Continuous, Pulser, or Repeater

- In generator modes (continuous or pulser), FINTERPOLATOR % FSYSREF = 0 must be ensured.

- SYSREF_DLY_BYP field must be configured appropriately for generator or repeater modes (a GUI autoset condition normally ensures this whenever SYSREF_MODE is set)

- SRREQ_VCM field should be set to DC-coupled mode for continuous or pulsed generator output. In repeater mode output, the SYSREF input may be AC- or DC-coupled and SRREQ_VCM should be set accordingly.

- For continuous mode, a HIGH signal must be seen on SYSREFREQ pins continuously. For pulsed generator mode, a LOW→HIGH transition must be seen on SYSREFREQ pins to trigger the pulser. For repeater mode, the output will follow the input state.

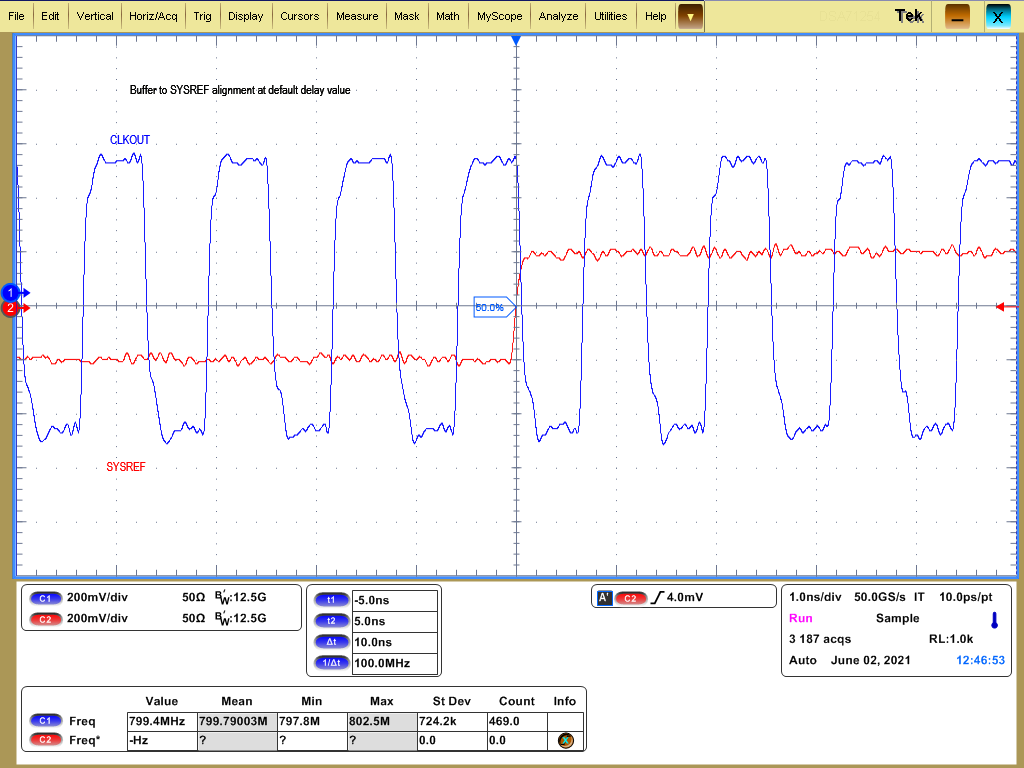

Figure 3-5 800-MHz Buffer Mode With SYSREF

Figure 3-5 800-MHz Buffer Mode With SYSREFThe SYSREF generator frequency is based on the CLKIN frequency, but the re-timing happens at the output frequency; consequently, the SYSREF generator still matches to the falling edge of the clock input even for multiplier and divider modes.

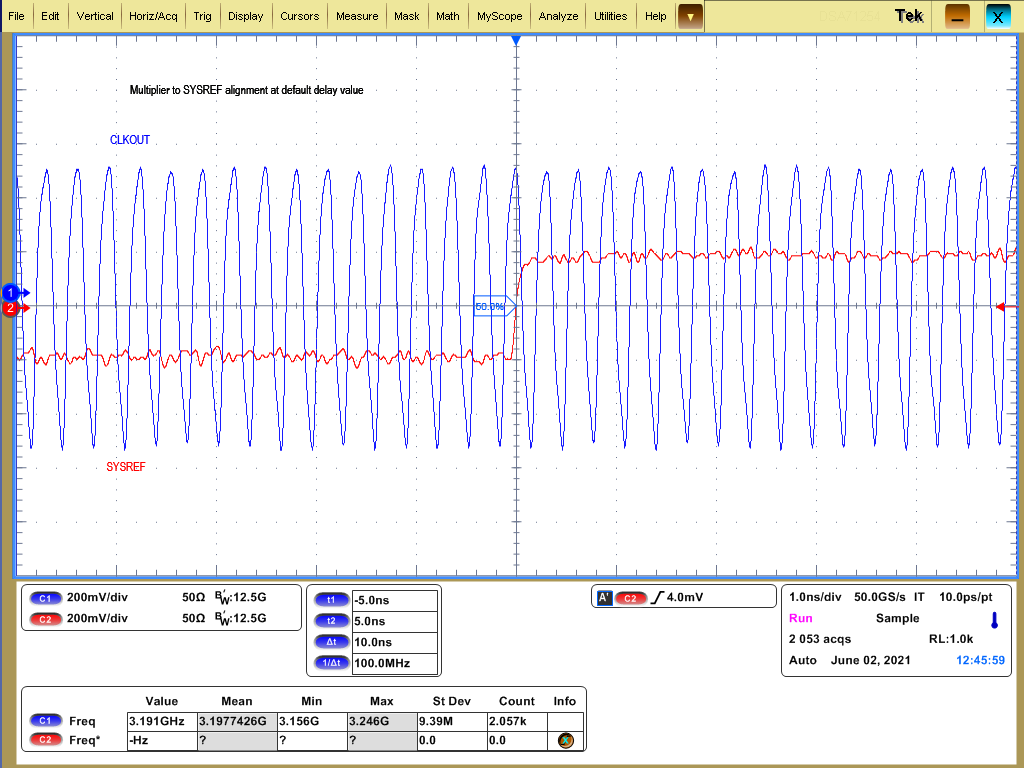

Figure 3-6 3200-MHz Multiplier Mode With CLKOUT, LOGICLK, and SYSREF

Figure 3-6 3200-MHz Multiplier Mode With CLKOUT, LOGICLK, and SYSREF