SNAU266A July 2021 – August 2022

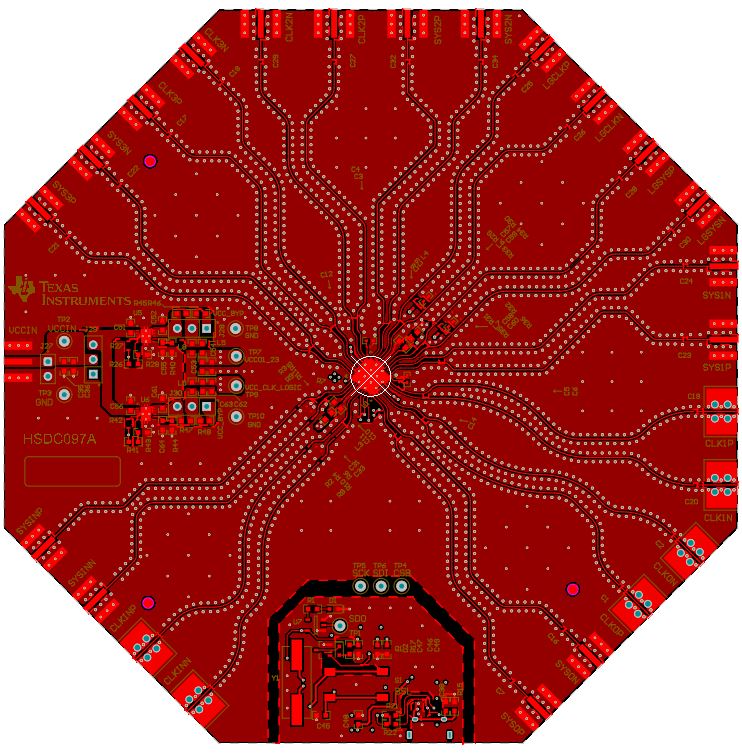

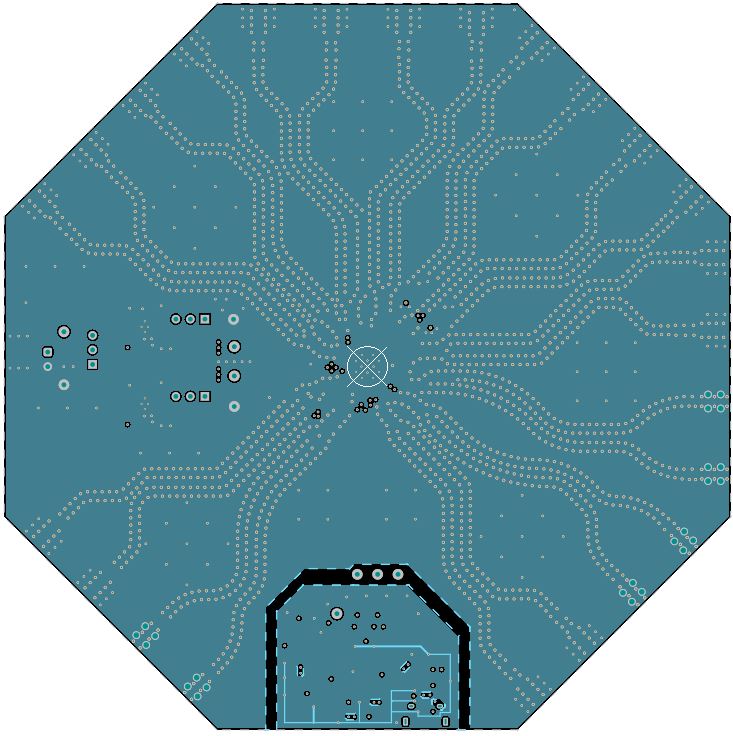

5.2 PCB Layout

Figure 5-2 PCB Layer Plot - Top Layer

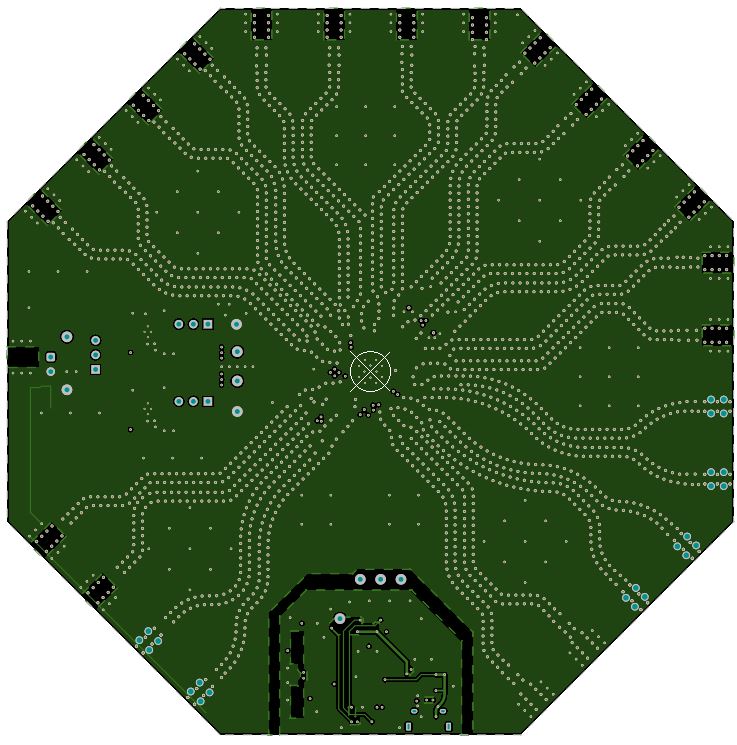

Figure 5-2 PCB Layer Plot - Top Layer Figure 5-3 PCB Layer Plot - Layer 2 (RF GND)

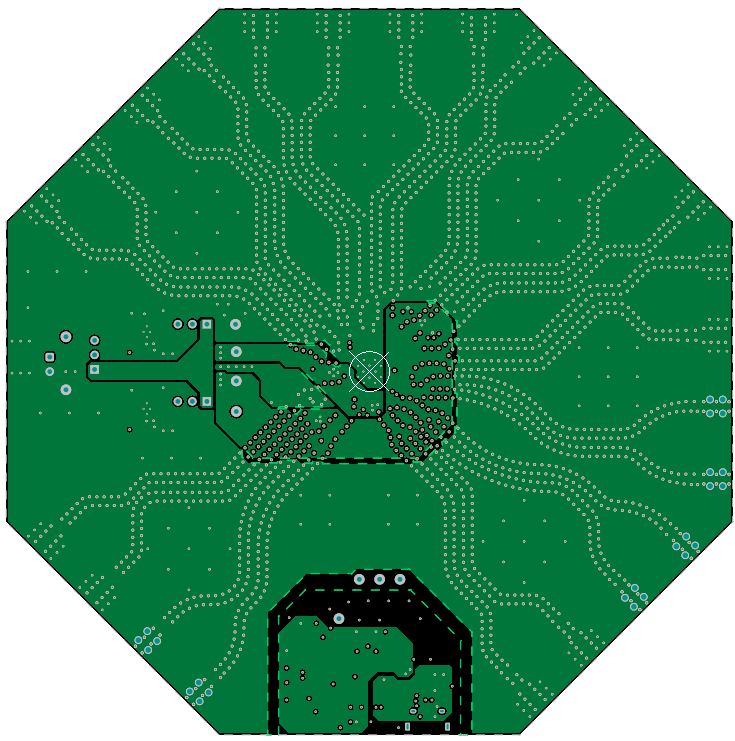

Figure 5-3 PCB Layer Plot - Layer 2 (RF GND) Figure 5-4 PCB Layer Plot - Layer 3 (Signal GND 1)

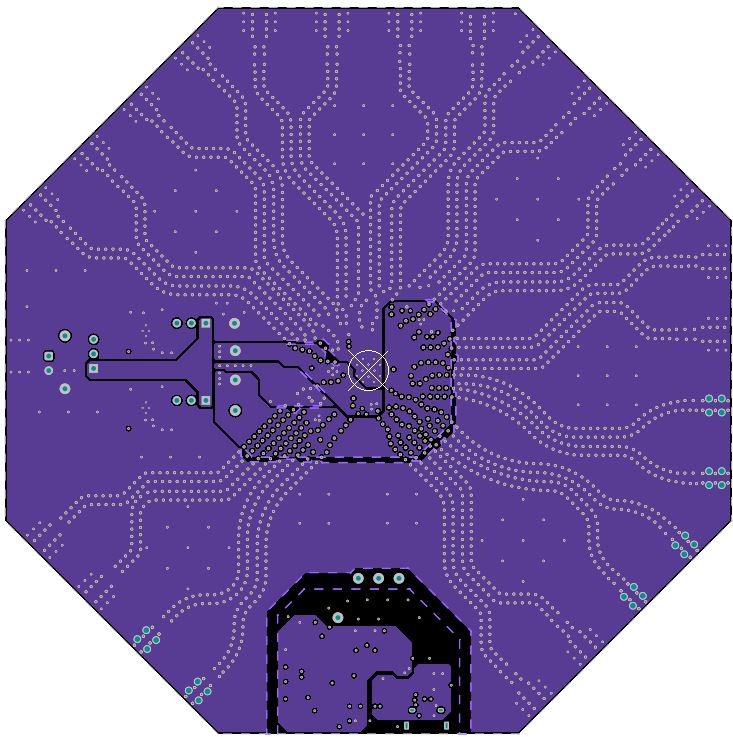

Figure 5-4 PCB Layer Plot - Layer 3 (Signal GND 1) Figure 5-5 PCB Layer Plot - Layer 4 (Signal GND 2)

Figure 5-5 PCB Layer Plot - Layer 4 (Signal GND 2) Figure 5-6 PCB Layer Plot - Layer 5 (GND)

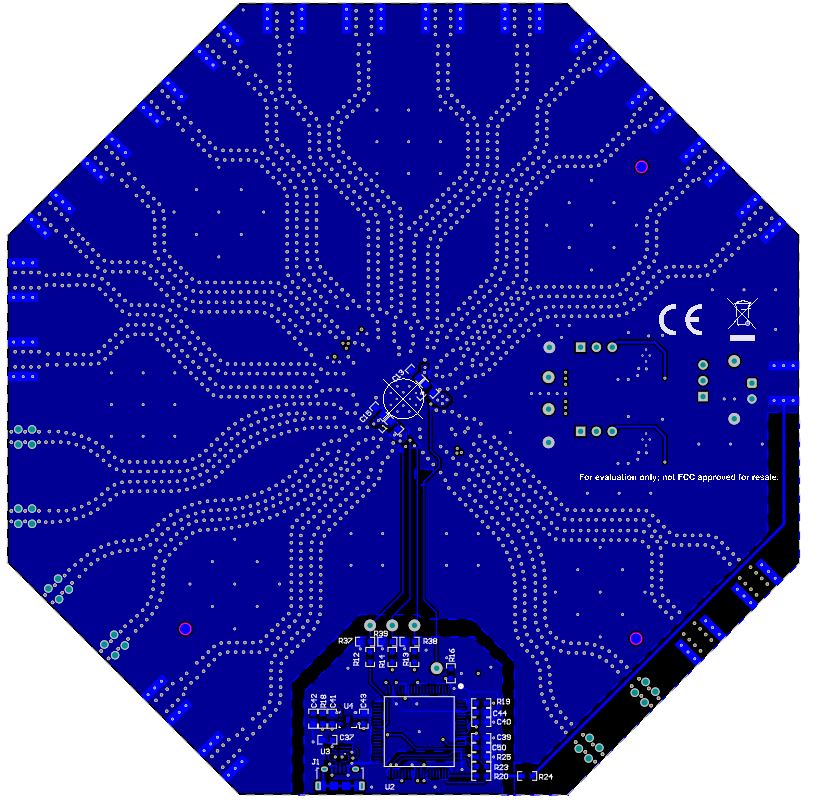

Figure 5-6 PCB Layer Plot - Layer 5 (GND) Figure 5-7 PCB Layer Plot - Bottom Layer

Figure 5-7 PCB Layer Plot - Bottom Layer