SLWU087E november 2013 – june 2023

- 1

- High Speed Data Converter Pro GUI

- Trademarks

- 1 Introduction

- 2 Software Start up

-

3 User Interface

- 3.1

Toolbar

- 3.1.1 File Options

- 3.1.2 Instrument Options

- 3.1.3 Data Capture Option

- 3.1.4

Test Options

- 3.1.4.1 Notch Frequency Bins

- 3.1.4.2 2 Channel Display and Cursor Lock

- 3.1.4.3 Analysis Window Markers

- 3.1.4.4 X-Scale in Time

- 3.1.4.5 Y-Scale in Voltage

- 3.1.4.6 Other Frequency Options

- 3.1.4.7 NSD Marker

- 3.1.4.8 Phase Plot

- 3.1.4.9 Phase in Degree

- 3.1.4.10 Histogram

- 3.1.4.11 Disable User Popups

- 3.1.4.12 HSDC Pro Lite Version

- 3.1.5 Help

- 3.2 Status Windows

- 3.3 Mode Selection

- 3.4 Device Selection

- 3.5 Skip Configuration

- 3.6 Capture Button (ADC Mode Only)

- 3.7 Test Selection (ADC Mode only)

- 3.8 DAC Display Panel (DAC Mode only)

- 3.9 I/Q Multi-Tone Generator

- 3.1

Toolbar

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW14J58 Functional Description

- 7 TSW14J57 Functional Description

- 8 TSW14J56 Functional Description

- 9 TSW14J50 Functional Description

- 10TSW14J10 Functional Description

- A Signal Processing in High Speed Data Converter Pro

- B History Notes

- C Revision History

3.1.3.3.4 Read Captured Memory from the Slave Board

Disconnect the HSDC Pro from master board, and connect the software to slave. The user must select the device under test on the slave board again as the GUI does not keep track when using multiple boards.

Once the device is selected from the drag down menu, the message in Figure 3-15 will occur. Click OK to continue.

Figure 3-15 Trigger Confirmation Window

Figure 3-15 Trigger Confirmation WindowIn the GUI main panel, enter the sampling rate for the correct FFT processing. Once this value is entered, the captured data from the trigger event is displayed.

For the TSW14J5x, there is an advanced option available for Master/Slave triggering that is synchronized with the SYSREF signal used by the JESD204B interface. This mode enables a Master/Slave triggering synchronized with SYSREF rising edges. In master mode, a hardware output trigger is generated on the TRIG_OUT_A/B/C SMAs at the first rising edge of SYSREF that occurs after the user presses the ‘Capture’ button. The data is captured at the next rising edge of SYSREF.

In the slave triggering mode, the capture occurs at the first SYSREF rising edge following the trigger input rising edge on the TRIG_IN SMA input. This way both Master and Slave will start capturing data at the same SYSREF edge in a Synchronized manner.

Software Changes Required: (The following steps are applicable for both ADC and DAC)

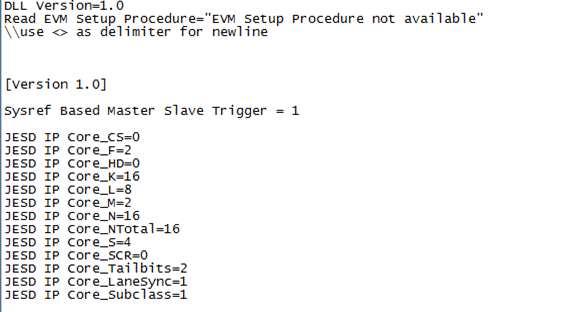

To put the TSW14J5x boards in Sysref-Based Master Slave Triggering mode, add the following INI parameter just below the [Version 1.0] entry in the corresponding master and slave device INI files, as shown in Figure 3-16.

- Sysref Based Master Slave Trigger = 1

Figure 3-16 Sysref-Based Master Slave Triggering INI Setting

Figure 3-16 Sysref-Based Master Slave Triggering INI SettingIn the HSDC Pro GUI, select the Trigger Option menu under Data Capture Options.

For the master board, select Trigger mode enable and Arm on next capture button press.

For the slave board, select Trigger mode enable in the Trigger Option window.

HSDC Pro GUI is now configured for SYSREF-Based Master Slave Triggering. Go back to the master board and the software will do a capture on the next rising edge detected on EXT_TRG_INPUT/TRIG_IN connectors after the user clicks on the "capture" button.